【11】證書號數：I665774

【45】公告日：中華民國 108 (2019) 年 07 月 11 日

【51】Int. Cl. : H01L23/492 (2006.01)

發明

全 5 頁

【54】名稱：電子封裝件及其製法

ELECTRONIC PACKAGE AND MANUFACTURING METHOD THEREOF

【21】申請案號：107128450 【22】申請日：中華民國 107 (2018) 年 08 月 15 日

【72】發明人：李泳達 (TW) LI, YUNG TA

【71】申請人：矽品精密工業股份有限公司 SILICONWARE PRECISION INDUSTRIES CO., LTD.

臺中市潭子區大豐路 3 段 123 號

【74】代理人：陳孚竹；張家彬

【56】參考文獻：

TW 201618256A CN 1697148A

CN 103745933B

審查人員：修宇鋒

【57】申請專利範圍

- 一種電子封裝件，係包括：一承載結構，係具有複數電性接點；以及一電子元件，係具有複數導電凸塊，以令該電子元件藉由該導電凸塊結合至該承載結構之該電性接點，其中，該導電凸塊之最大平面寬度係小於 25 微米，且該電性接點或該導電凸塊之其中一者係形成有複數尖部，以插入至該電性接點或該導電凸塊之另一者中。

- 如申請專利範圍第 1 項所述之電子封裝件，其中，該電性接點或該導電凸塊之其中一者係形成有粗糙面，其中，該粗糙面具有複數該尖部。

- 如申請專利範圍第 1 項所述之電子封裝件，其中，該複數尖部之間係具有高度差。

- 如申請專利範圍第 3 項所述之電子封裝件，其中，該高度差係小於 1.5 微米。

- 如申請專利範圍第 1 項所述之電子封裝件，其中，該尖部上形成有表面處理層。

- 一種電子封裝件之製法，係包括：提供一具有複數電性接點之承載結構及一具有複數導電凸塊之電子元件，其中，該電性接點或該導電凸塊之其中一者係形成有複數尖部，且該導電凸塊之最大平面寬度係小於 25 微米；以及將該電子元件藉由該導電凸塊結合該承載結構之該電性接點，以令該電性接點或該導電凸塊之其中一者之該尖部插入該電性接點或該導電凸塊之另一者中。

- 如申請專利範圍第 6 項所述之電子封裝件之製法，其中，該電性接點或該導電凸塊之其中一者係形成有粗糙面，其中，該粗糙面具有複數該尖部。

- 如申請專利範圍第 6 項所述之電子封裝件之製法，其中，該複數尖部之間係具有高度差。

- 如申請專利範圍第 8 項所述之電子封裝件之製法，其中，該高度差係小於 1.5 微米。

- 如申請專利範圍第 6 項所述之電子封裝件之製法，復包括形成表面處理層於該尖部上。

圖式簡單說明

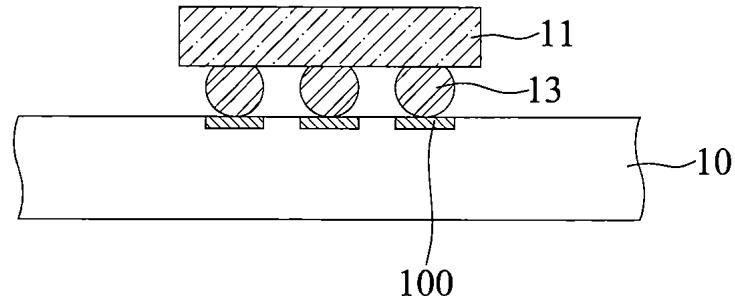

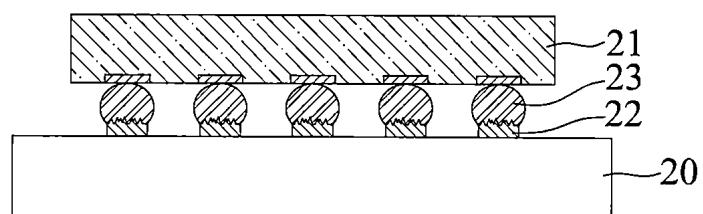

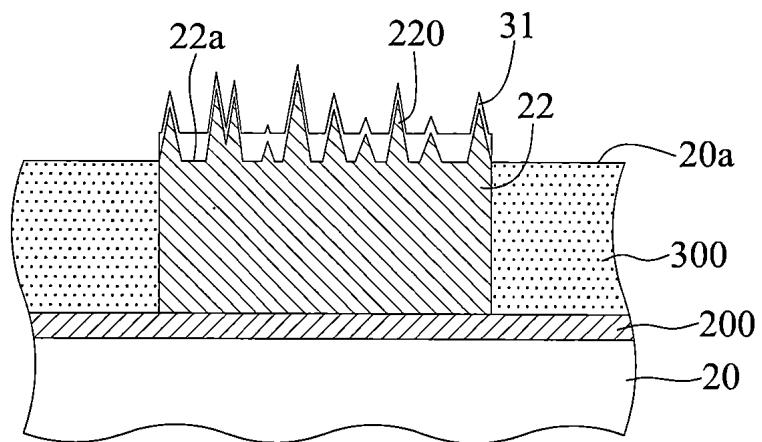

第 1A 至 1B 圖係為習知覆晶式封裝結構之製法的剖視示意圖。

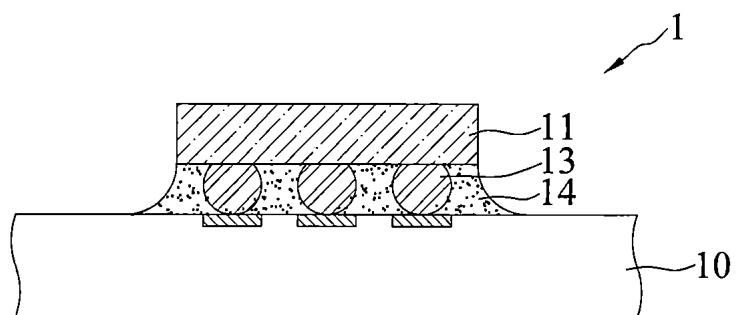

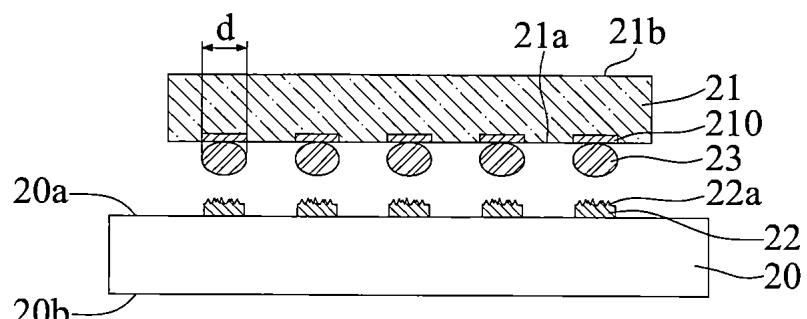

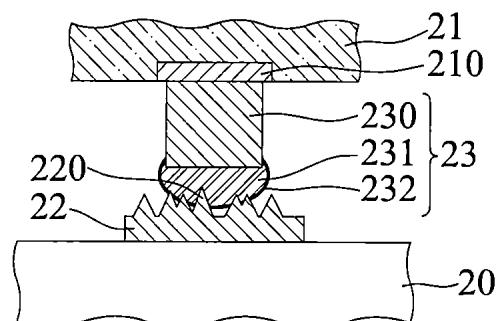

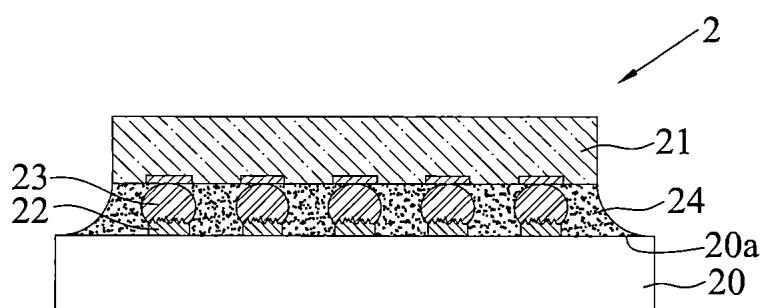

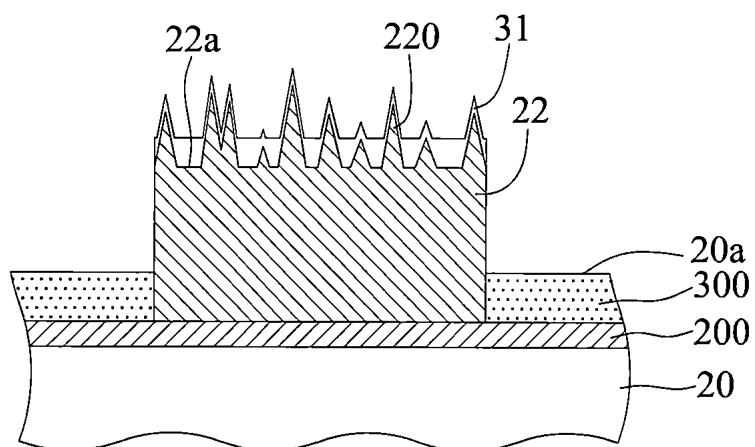

第 2A 至 2C 圖係為本發明之電子封裝件之製法之剖視示意圖。

(2)

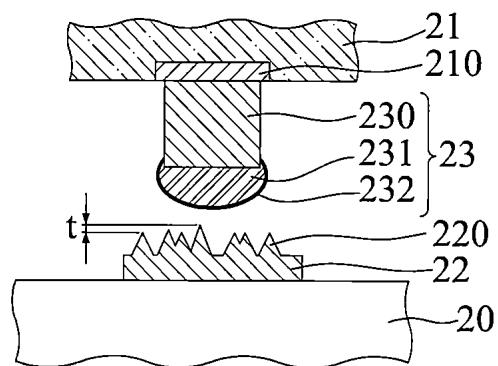

第 2A' 圖係為第 2A 圖之局部放大剖視圖。

第 2B'，圖係為第 2B 圖之局部放大剖視圖。

第 2C'，圖係為第 2C 圖之局部放大剖視圖。

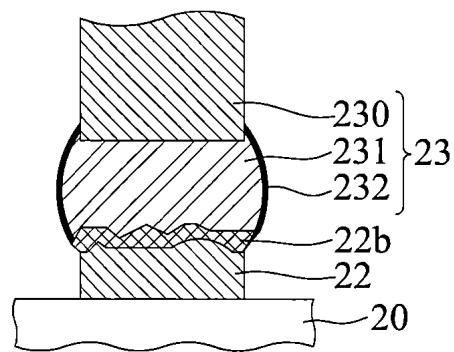

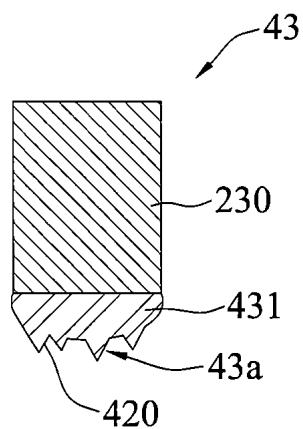

第 3A 及 3B 圖係為第 2A 圖之承載結構之不同實施例之局部放大剖視圖。

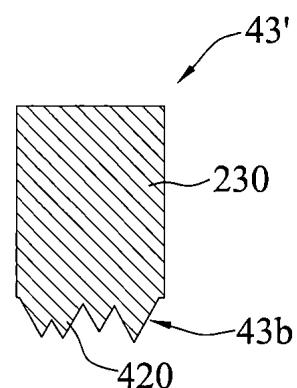

第 4A 及 4B 圖係為第 2A 圖之電子元件之不同實施例之局部放大剖視圖。

## 【第1A圖】

## 【第1B圖】

## 【第2A圖】

(3)

【第2A'圖】

【第2B圖】

【第2B'圖】

【第2C圖】

(4)

【第2C'圖】

【第3A圖】

【第3B圖】

(5)

【第4A圖】

【第4B圖】