【11】證書號數：I665741

【45】公告日：中華民國 108 (2019) 年 07 月 11 日

|                |                            |                             |

|----------------|----------------------------|-----------------------------|

| 【51】Int. Cl. : | <i>H01L21/50 (2006.01)</i> | <i>H01L21/58 (2006.01)</i>  |

|                | <i>H01L23/00 (2006.01)</i> | <i>H01L23/538 (2006.01)</i> |

發明

全 12 頁

## 【54】名稱：一種半導體封裝結構及其製造方法

A SEMICONDUCTOR PACKAGE AND A MANUFACTURING METHOD

THEREOF

【21】申請案號：104140466

【22】申請日：中華民國 104 (2015) 年 12 月 03 日

【11】公開編號：201721769

【43】公開日期：中華民國 106 (2017) 年 06 月 16 日

【72】發明人：陳宗熙 (TW) CHEN, ZONG-XI；劉欣茂 (TW) LIU, HSIN-MAO；謝明勳 (TW)

HSIEH, MIN-HSUN【71】申請人：晶元光電股份有限公司 EPISTAR CORPORATION

新竹市東區新竹科學工業園區力行路 21 號

## 【56】參考文獻：

TW 201521239

TW 201721769

審查人員：邱智強

## 【57】申請專利範圍

1. 一種半導體封裝結構，包括：一載板；一第一複合金屬層，包含一第一金屬層及一與該第一金屬層和該載板直接接觸的第二金屬層，且該第一金屬層與該第二金屬層包含不同的金屬；一第一接合材料層，包含銀且不包含鉛與錫，並直接接觸該第一金屬層；一晶粒，位於該第一接合材料層上；一第二複合金屬層，包含一第三金屬層及一與該載板直接連接的第四金屬層；一散熱器，位於該第二複合金屬層下方；以及一第二接合材料層，位於該第二複合金屬層與該散熱器之間，並直接接觸該第二複合金屬層，其中，該第三金屬層與該第四金屬層直接接觸並包含不同金屬。

2. 如申請專利範圍第 1 項所述的半導體封裝結構，其中，該第一接合材料層，其熱阻值大於 120W/mk、或其體積電阻大於  $10^{-7}$  歐姆-公分、或其接合強度介於 3~5Kgf。

3. 如申請專利範圍第 1 項所述的半導體封裝結構，其中，該載板包括一陶瓷材料層。

4. 如申請專利範圍第 1 項所述的半導體封裝結構，其中，該第一複合金屬層與該第二複合金屬層包含相同金屬。

5. 如申請專利範圍第 1 項所述的半導體封裝結構，其中該載板的垂直投影面積等於或大於該晶粒的垂直投影面積。

6. 如申請專利範圍第 1 項所述的半導體封裝結構，其中，該散熱器更包括一散熱板及複數個導電接腳，該散熱板及該複數個導電接腳設置於該載板下，且該晶粒與該等導電接腳電性連接。

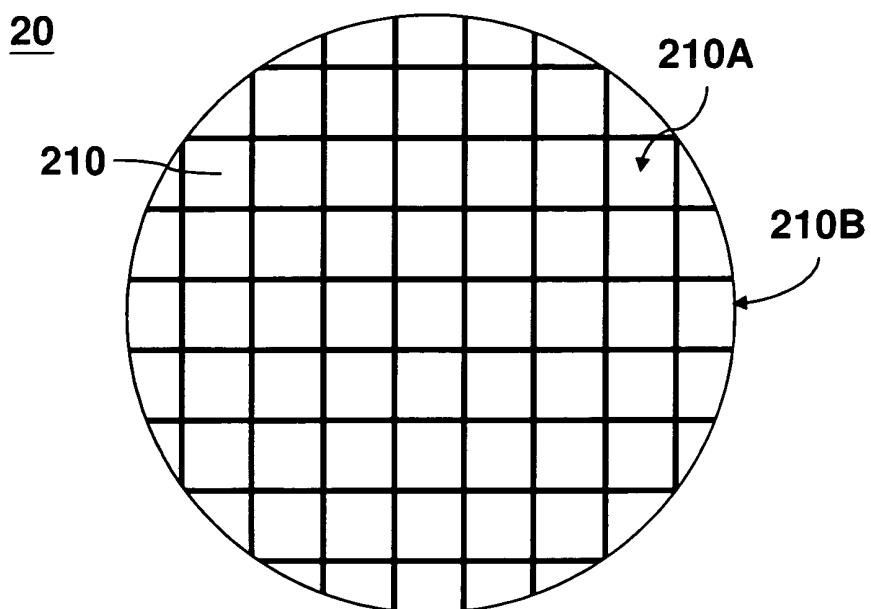

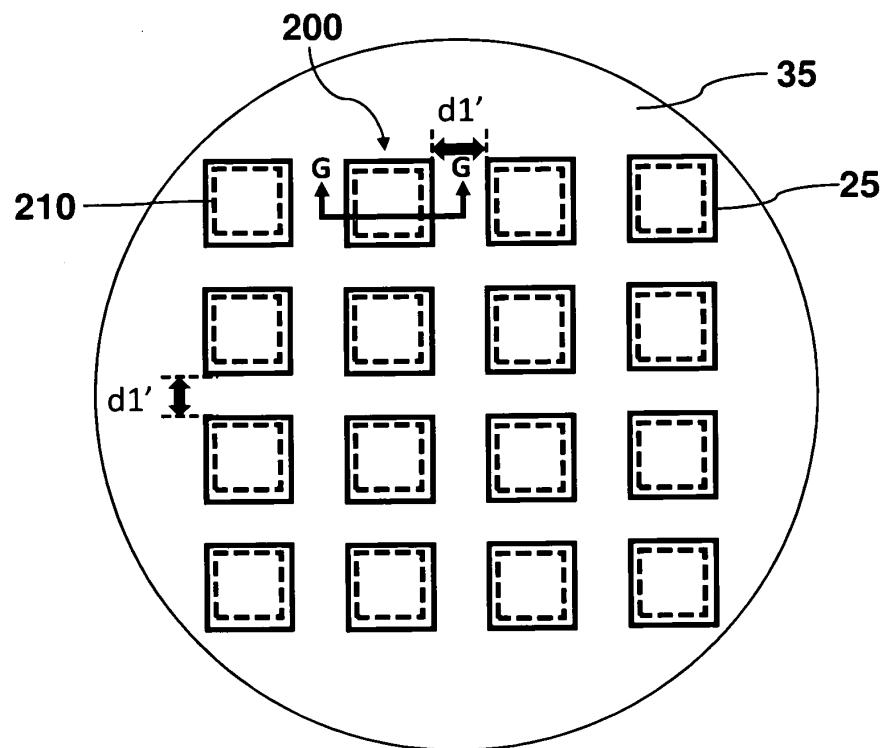

7. 一種半導體封裝結構的製造方法，其步驟包括：提供複數個晶粒，且各個該等晶粒具有相對的第一上表面及一第一下表面；提供一第一暫時性基板，並使各個該等晶粒以該第一下表面固定於該第一暫時性基板上；擴張該等晶粒彼此間的距離至一預定距離  $d_1$ ， $d_1 > 0$ ；提供一第二暫時性基板，使得各個該等晶粒的該第一上表面朝向該第二暫時性基板；提供一載板，其具有相對的一第二上表面及一第二下表面；形成一無鉛錫的第一接合材料層於該第二上表面上；藉由該無鉛錫的第一接合材料層使各個該等晶粒的該第一

上表面與該載板的該第二上表面接合；去除該第二暫時性基板；以及切割該載板，形成複數個半導體封裝體，其中，各個該複數個半導體封裝體包括一次載板，且該次載板之垂直投影面積大於該等晶粒中之一的垂直投影面積。

8. 如申請專利範圍第 7 項所述的半導體封裝結構的製造方法，其中，該載板更包括一陶瓷材料層夾於一第一複合金屬層與一第二複合金屬層之間，該第一複合金屬層包括一第一黏附層以及一第一高導電層，且該第一黏附層是夾於該陶瓷材料層與該第一高導電層之間，而該第二複合金屬層包括一第二黏附層以及一第二高導電層，且該第二黏附層是夾於該陶瓷材料層與該第二高導電層之間。

9. 如申請專利範圍第 7 項所述的半導體封裝結構的製造方法，其中，該第二暫時性基板包含一對熱或特定波長光線敏感的黏著層。

#### 圖式簡單說明

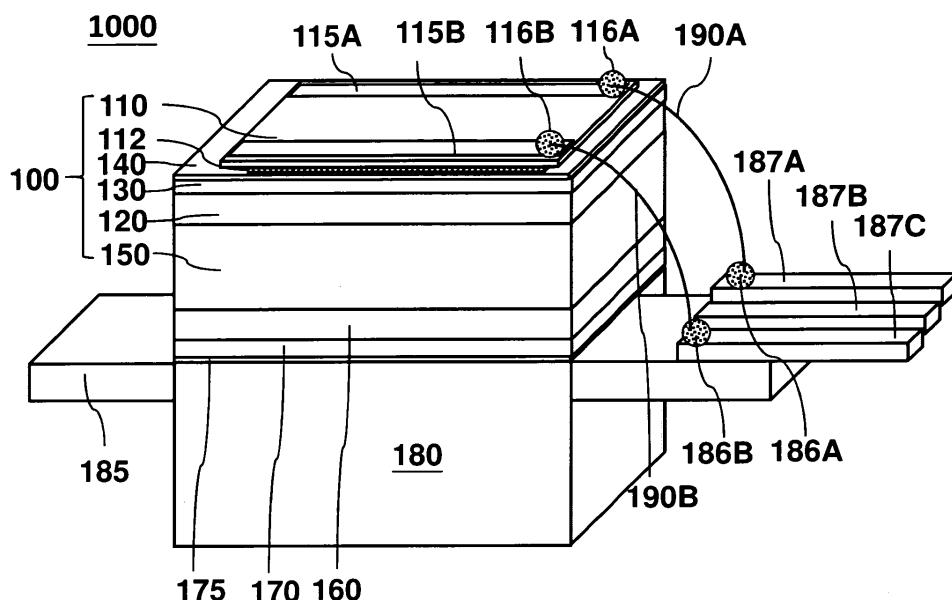

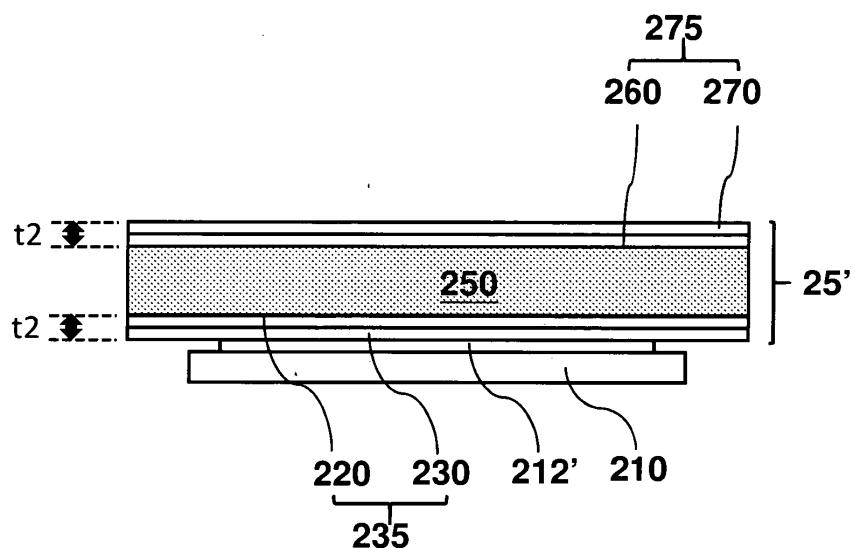

第 1A 圖~第 1B 圖顯示的是習知的一種半導體封裝結構。

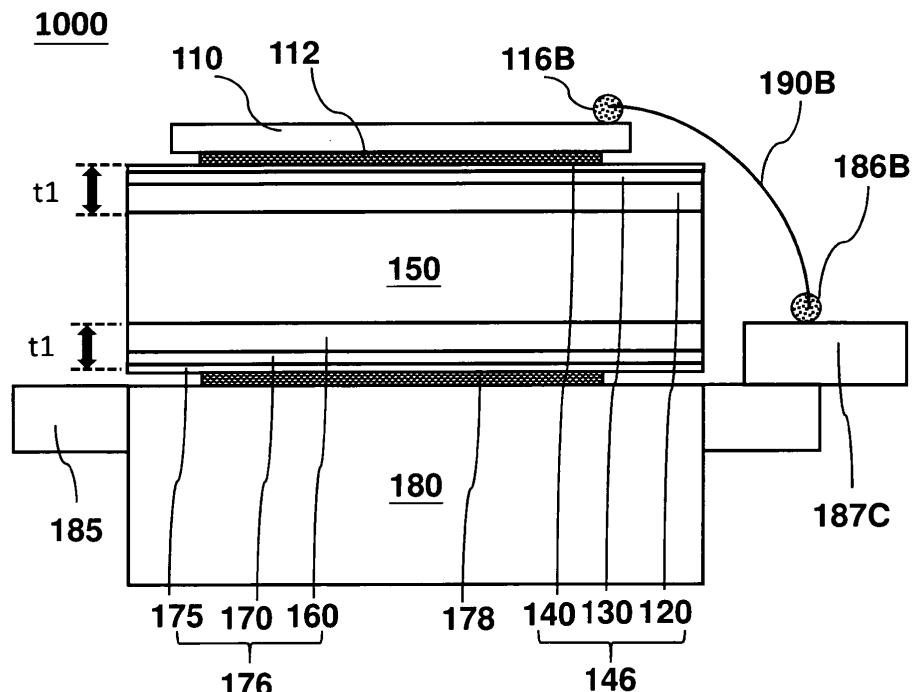

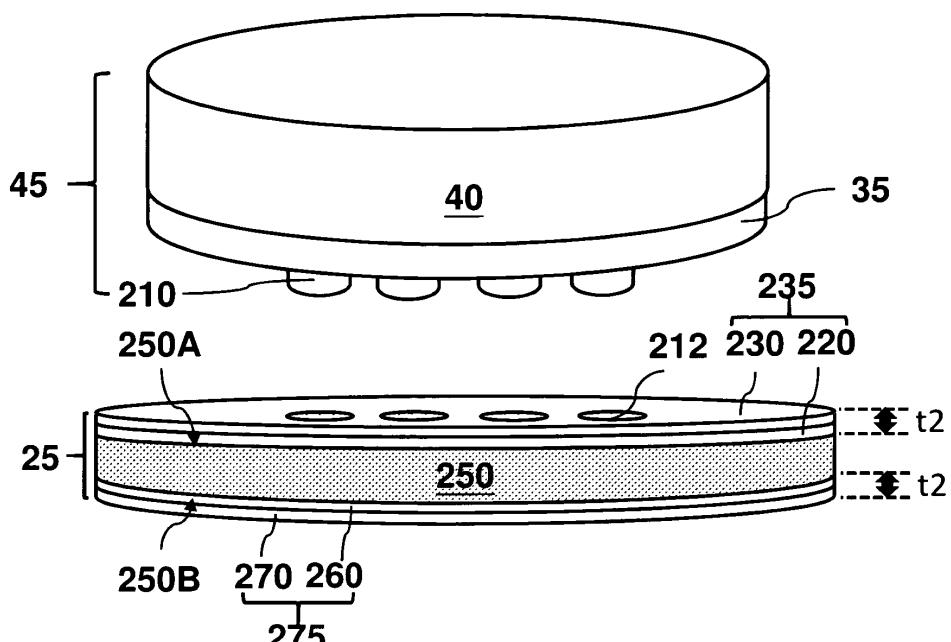

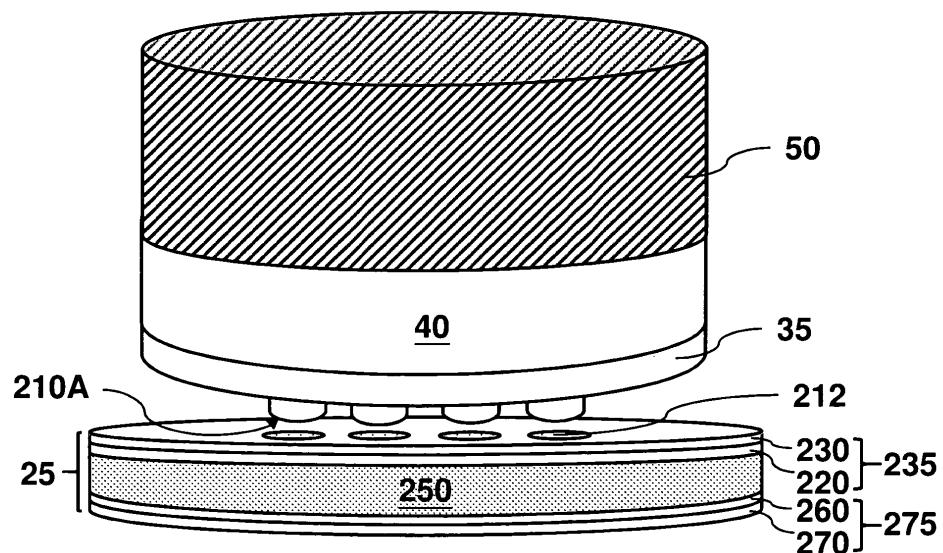

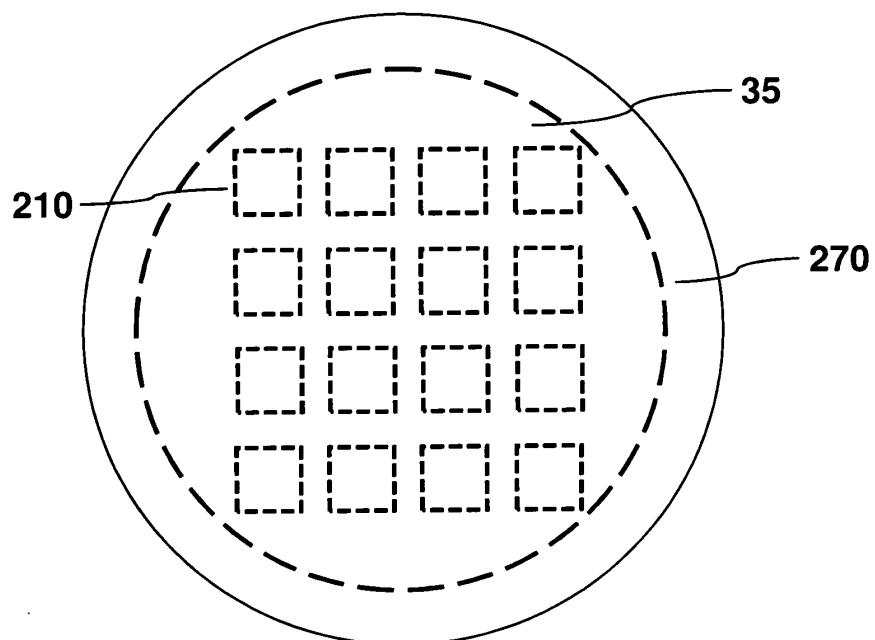

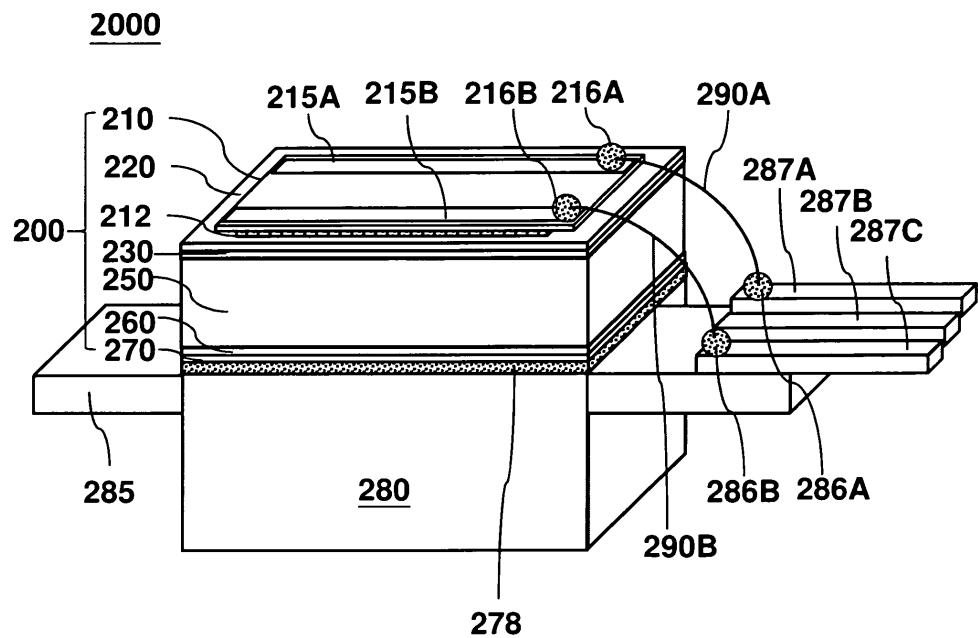

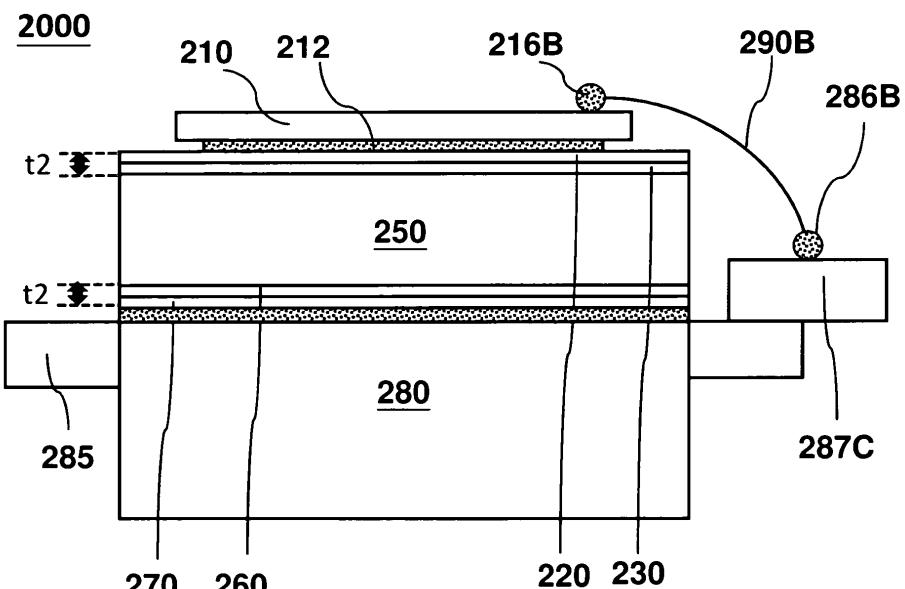

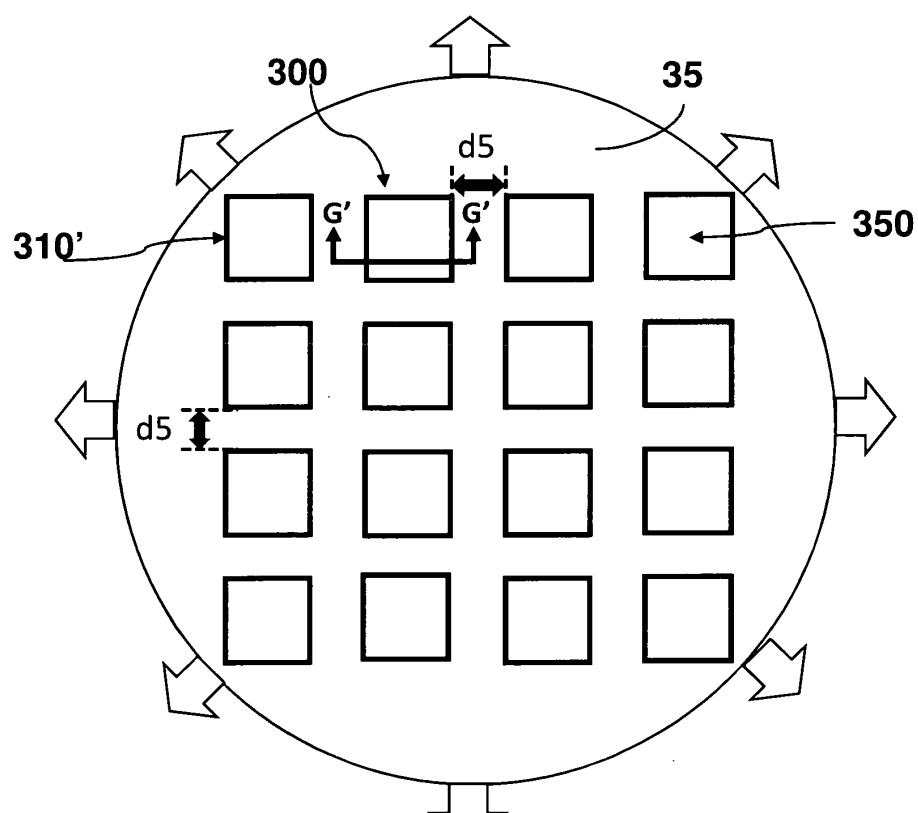

第 2A 圖~第 2G 圖顯示的是根據本發明一實施例的半導體封裝結構及其製造方法。

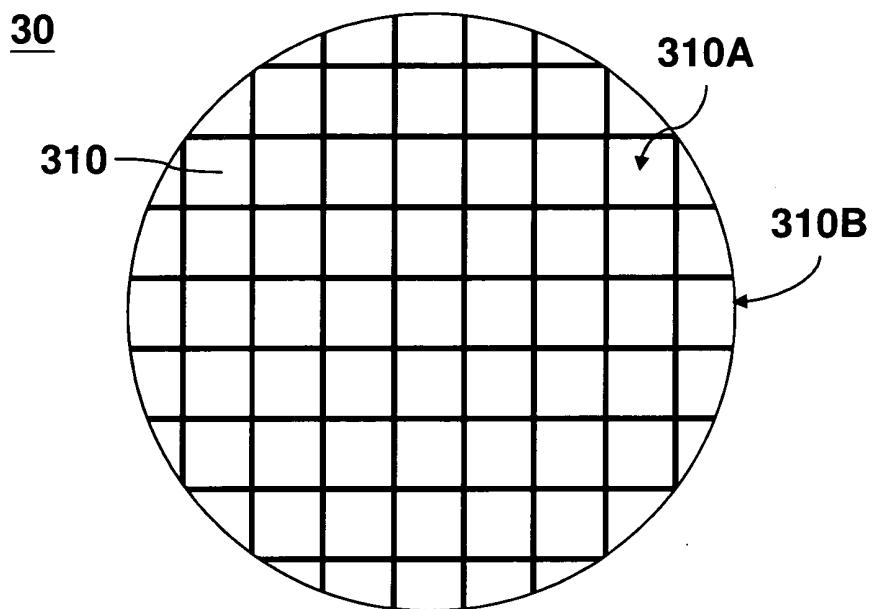

第 3A 圖~第 3B 圖顯示的是根據本發明一實施例的半導體封裝結構及其製造方法。

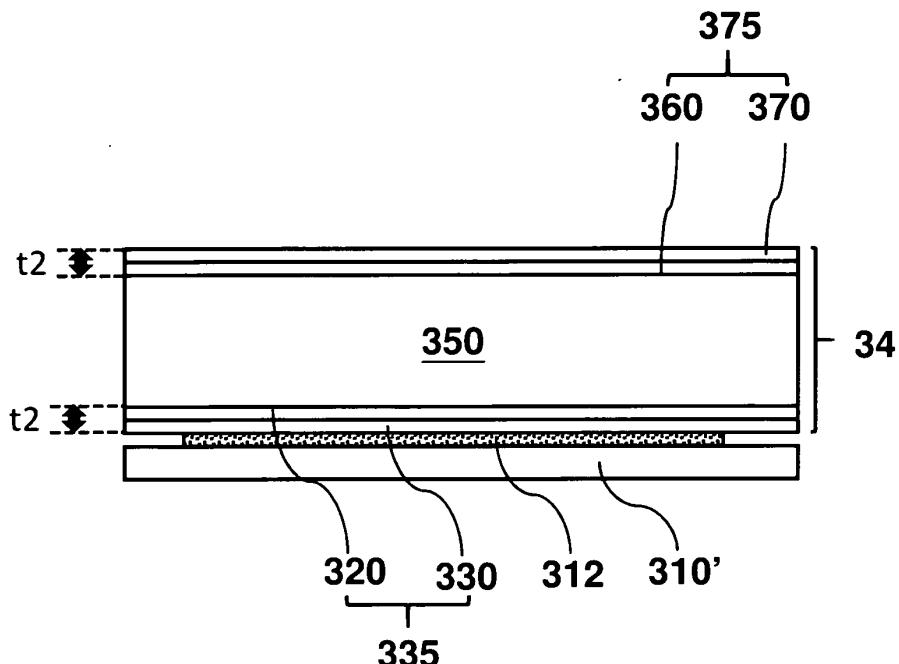

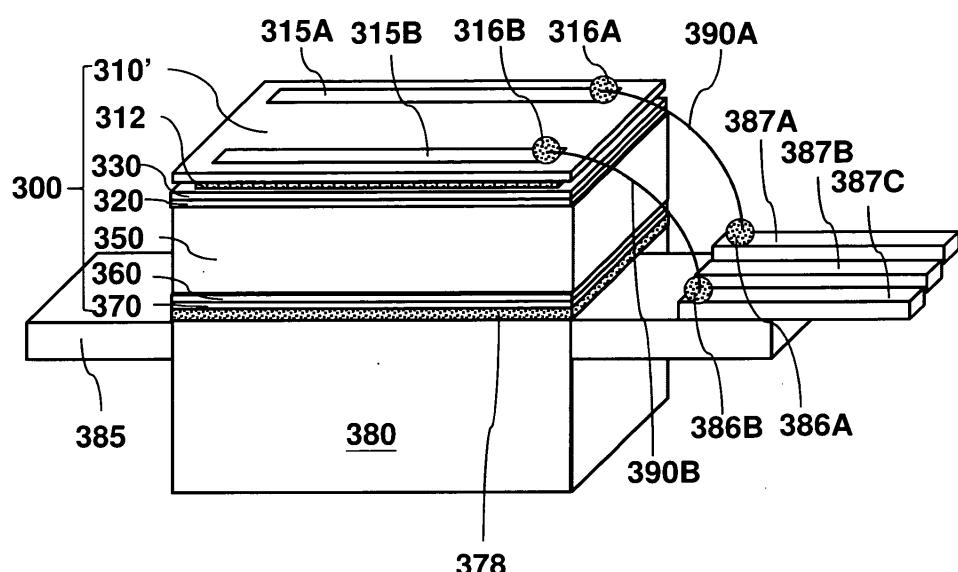

第 4A 圖~第 4G 圖顯示的是根據本發明一實施例的半導體封裝結構及其製造方法。

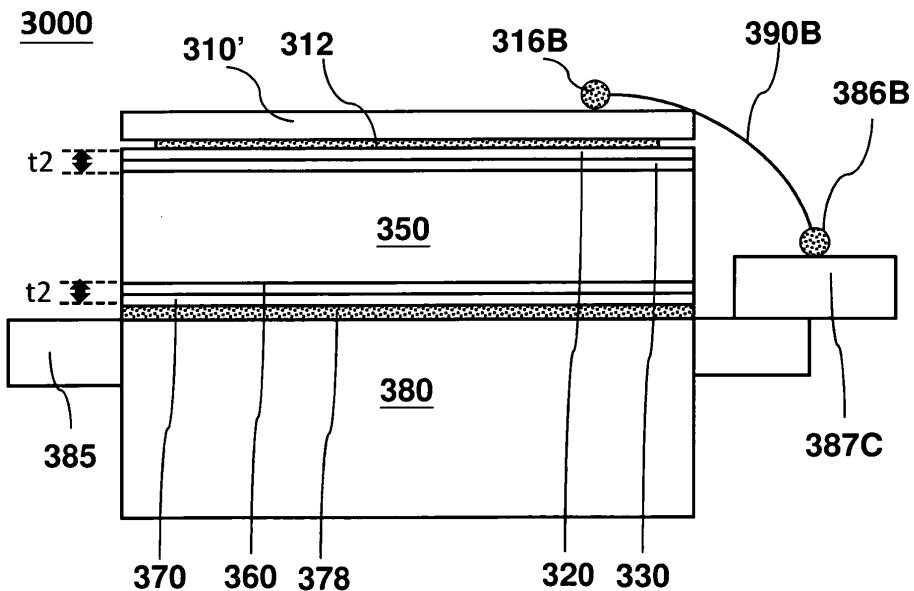

第 5A 圖~第 5B 圖顯示的是根據本發明一實施例的半導體封裝結構及其製造方法。

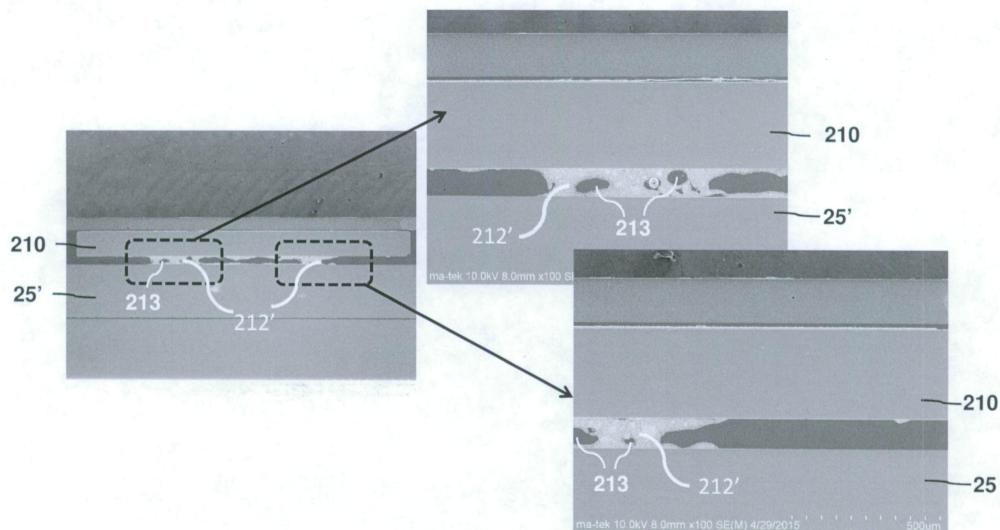

第 6 圖顯示的是如第 2G 圖所示的半導體封裝體 200 的晶粒 210、第一接合層 212 與載板 25 的接合面 SEM 照片。

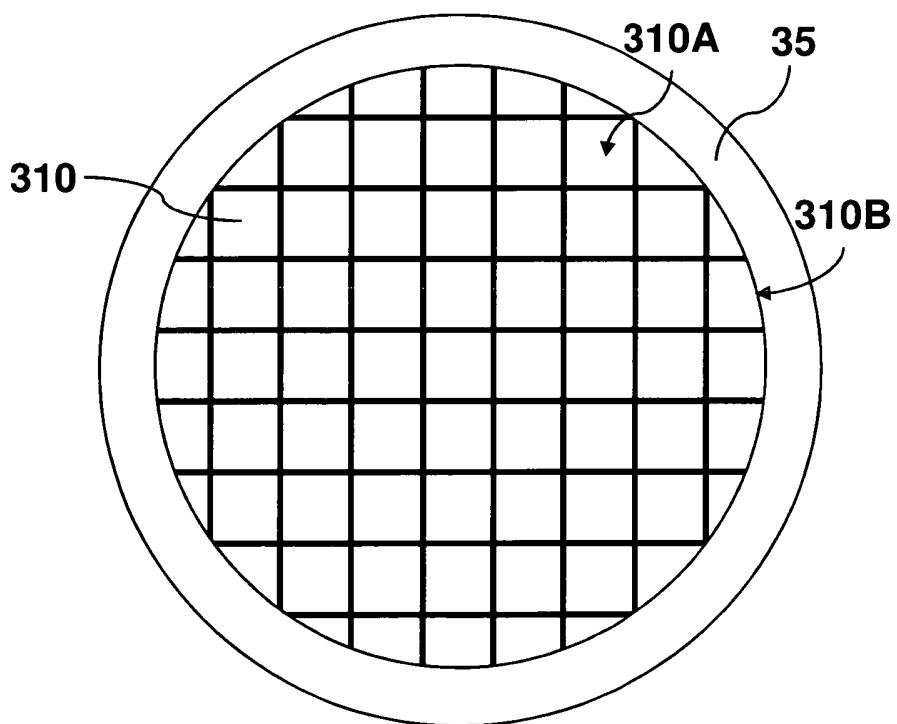

**第 1A 圖**

(3)

第 1B 圖

第 2A 圖

(4)

第 2B 圖

第 2C 圖

(5)

第 2D 圖

第 2E 圖

(6)

第 2F 圖

200

第 2G 圖

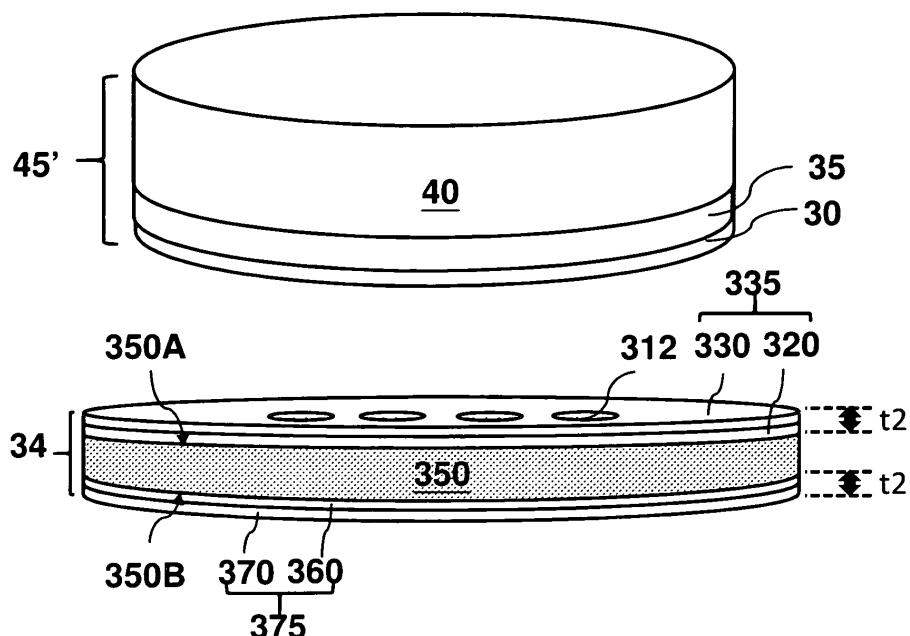

第 3A 圖

第 3B 圖

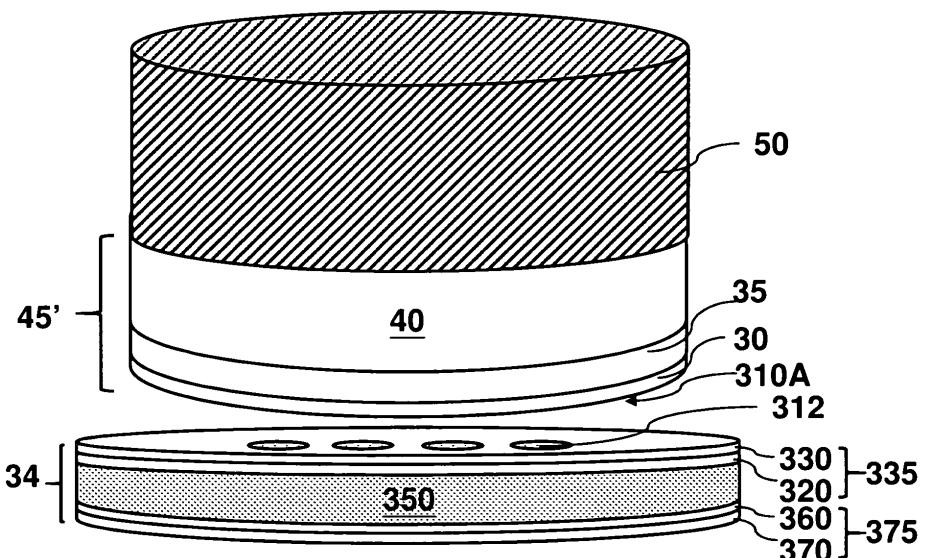

第 4A 圖

第 4B 圖

(9)

第 4C 圖

第 4D 圖

(10)

第 4E 圖

第 4F 圖

300

第 4G 圖

3000

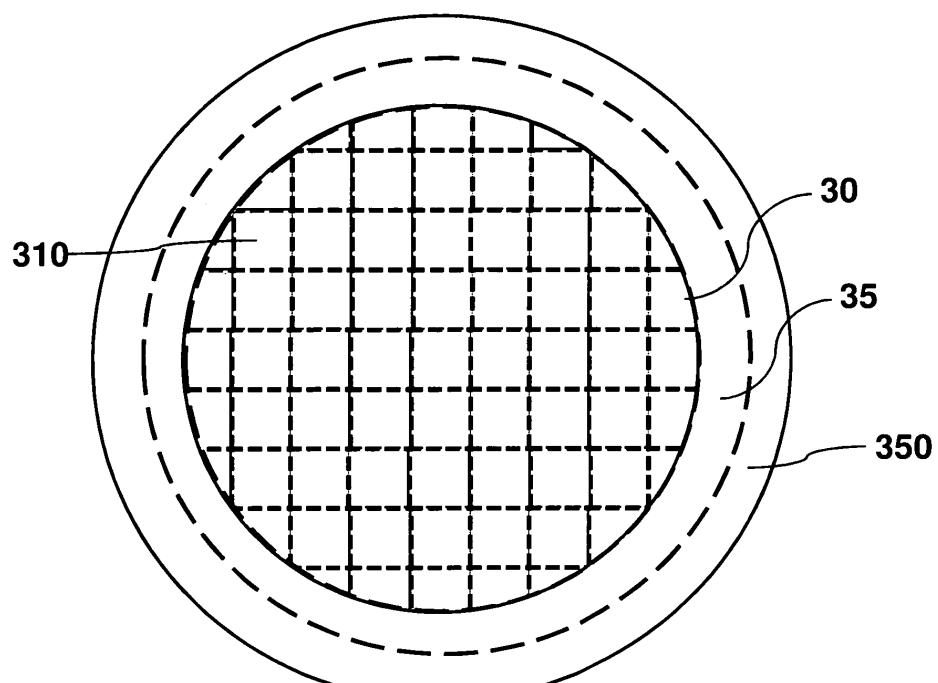

第 5A 圖

第 5B 圖

第 6 圖