【11】證書號數：I664708

【45】公告日：中華民國 108 (2019) 年 07 月 01 日

【51】Int. Cl. : H01L23/544 (2006.01)

H01L21/78 (2006.01)

發明

全 9 頁

【54】名稱：標記一半導體封裝之方法

METHOD OF MARKING A SEMICONDUCTOR PACKAGE

【21】申請案號：104142357

【22】申請日：中華民國 104 (2015) 年 12 月 16 日

【11】公開編號：201633491

【43】公開日期：中華民國 105 (2016) 年 09 月 16 日

【30】優先權：2014/12/16

美國 62/092,322

【72】發明人：斯坎倫克里斯托弗 M (US) SCANLAN, CHRISTOPHER M.

【71】申請人：戴卡科技有限公司

DECA TECHNOLOGIES INC.

美國

【74】代理人：李世章；彭國洋

【56】參考文獻：

US 6270712B1

US 8415260B2

US 2005/0017353A1

US 2005/0048681A1

US 2012/0195562A1

US 2013/0049580A1

US 2013/0280826A1

審查人員：于若天

【57】申請專利範圍

- 一種製作一半導體裝置之方法，該方法包含以下步驟：提供一晶圓，該晶圓包含複數個半導體晶粒，其中各半導體晶粒包含一作用表面(active surface)及一背側，該背側與該作用表面相對立；用一塗佈機器形成一多膜材料於該晶圓上方及該晶圓內的該複數個半導體晶粒之各者之該背側上方，該多膜材料包含一非光敏層及一光敏層，其中該光敏層之一厚度小於或等於該非光敏層之一厚度；用一數位曝光機器及一顯影劑藉由移除該光敏層之一部分，在用於該複數個半導體晶粒之各者的該光敏層內形成一識別標記，該識別標記編碼唯一產品資訊；固化該光敏層；及單切該晶圓成複數個半導體裝置。

- 如請求項 1 之方法，其中該晶圓係一原生半導體晶圓(native semiconductor wafer)。

- 如請求項 1 之方法，其中該晶圓係一經重構晶圓或經重構板材(panel)。

- 如請求項 1 之方法，其進一步包含形成具有一特徵大小的該等識別標記，該特徵大小在長度、寬度或兩者方面小於或等於 150 微米。

- 如請求項 1 之方法，其進一步包含以下步驟：形成該多膜材料，該多膜材料包含在 10 微米至 60 微米之範圍內之一厚度；及形成具有在 2 微米至 30 微米之範圍內之一厚度的用於該複數個半導體晶粒之各者的該等識別標記。

- 如請求項 1 之方法，其中用於在該晶圓上方形成該多膜材料的該塗佈機器進一步包含一膜貼合機、一旋轉塗佈機、一簾塗佈機、或一槽模塗佈機(slot die coater)。

- 如請求項 1 之方法，其進一步包含以下步驟：形成具有約 300 毫米之一直徑的該晶圓；且針對包含約 300mm 之一直徑的晶圓，依等於或大於 25 個晶圓/小時(WPH)之一速率，形成用於該複數個半導體晶粒之各者的該識別標記。

- 一種製作一半導體裝置之方法，該方法包含以下步驟：提供一晶圓，該晶圓包含複數個半導體晶粒，其中各半導體晶粒包含一作用表面及一背側，該背側與該作用表面相對

立；形成一多膜材料於該晶圓上方及該晶圓內的該複數個半導體晶粒之各者之該背側上方，該多膜材料包含一非光敏層及一光敏層；用一數位曝光機器及一顯影劑藉由移除該光敏層之一部分而不暴露該複數個半導體晶粒之各者之該背側，在用於該複數個半導體晶粒之各者的該光敏層中形成一唯一識別標記；固化該光敏層；及單切該晶圓成複數個半導體裝置。

9. 如請求項 8 之方法，其中該晶圓係一原生半導體晶圓，或一經重構晶圓或經重構板材。

10. 如請求項 8 之方法，其進一步包含形成具有一特徵大小的該等識別標記，該特徵大小在長度、寬度或兩者方面小於或等於 150 微米。

11. 如請求項 8 之方法，其中該多膜材料形成於該晶圓內的該複數個半導體晶粒之各者之該背側上。

12. 一種製作一半導體裝置之方法，該方法包含以下步驟：提供一晶圓，該晶圓包含複數個半導體晶粒，其中各半導體晶粒包含一作用表面及一背側，該背側與該作用表面相對立；形成一多膜材料於該晶圓上方且於該複數個半導體晶粒之各者上方，該多膜材料包含一非光敏層及一光敏層；及藉由在不使用一雷射的情況下移除該光敏層之一部分，在用於該複數個半導體晶粒之各者的該光敏層內形成一識別標記。

13. 如請求項 12 之方法，其中該晶圓係一原生半導體晶圓，或一經重構晶圓或經重構板材。

14. 如請求項 12 之方法，其進一步包含形成具有一特徵大小的該等識別標記，該特徵大小在長度、寬度或兩者方面小於或等於 150 微米。

15. 如請求項 12 之方法，其中該多膜材料形成於該晶圓內的該複數個半導體晶粒之各者之該背側上。

16. 如請求項 12 之方法，其進一步包含形成具有小於或等於該多膜材料之一厚度之 50 百分比的一厚度的該識別標記。

#### 圖式簡單說明

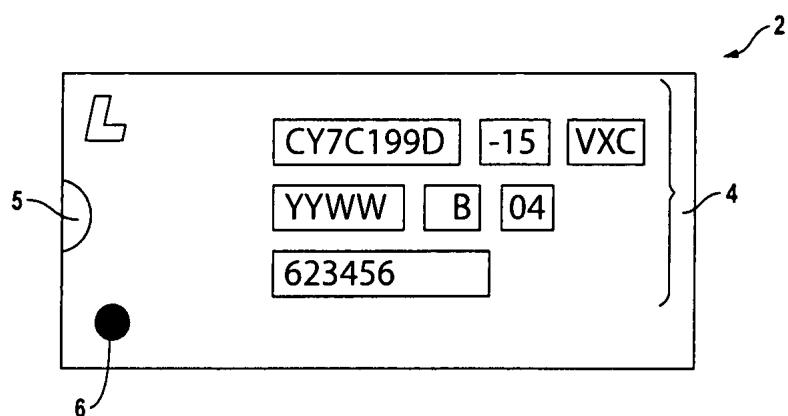

圖 1 繪示如先前技術中已知之半導體封裝上之標記。

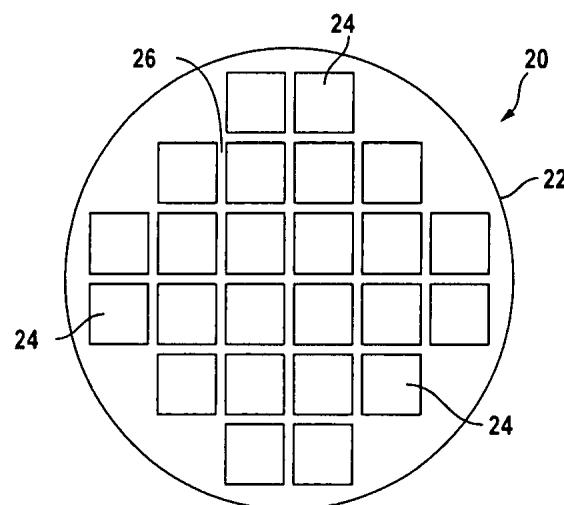

圖 2A 至圖 2E 繪示一半導體晶圓，其包含複數個半導體晶粒。

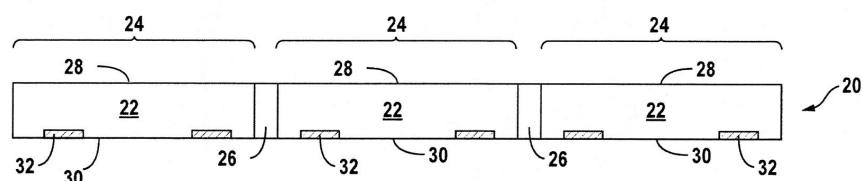

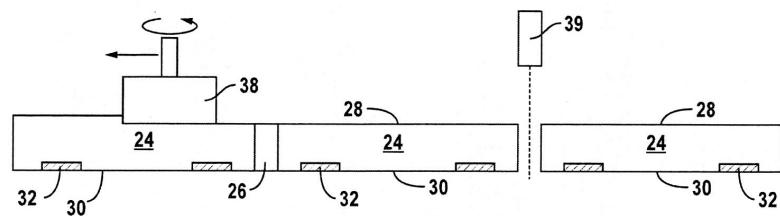

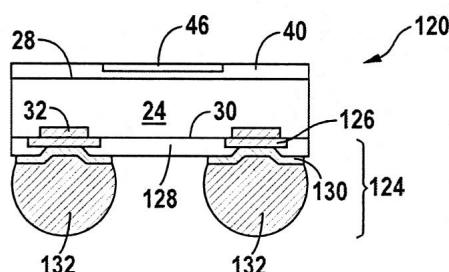

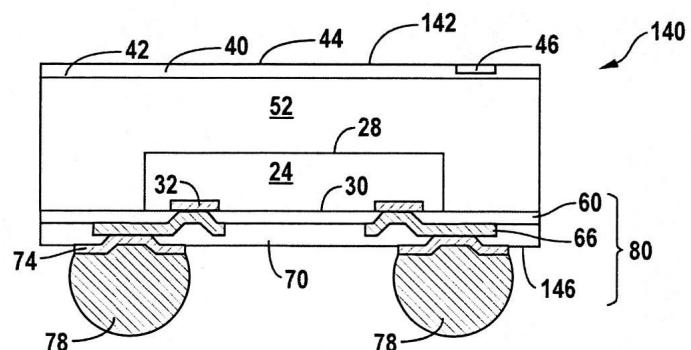

圖 3A 至圖 3F 繪示具有一識別標記之半導體封裝之態樣，及一種提供識別標記之方法。

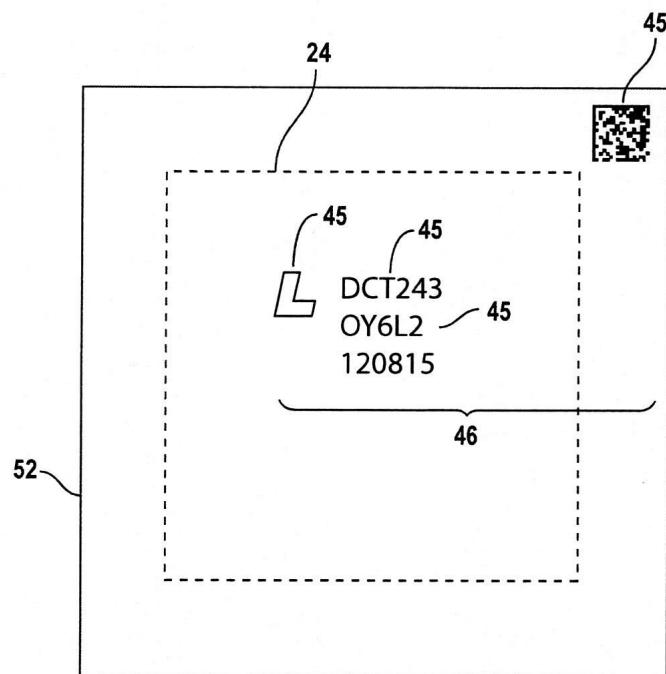

圖 4 繪示包含一識別標記之一半導體封裝之一實施例。

圖 5 繪示包含複數個半導體封裝之一晶圓之一實施例，該複數個半導體封裝包含識別標記。

圖 6 繪示包含複數個半導體封裝之一晶圓之一實施例，該複數個半導體封裝包含識別標記。

圖 7 繪示包含一識別標記之一半導體封裝之一實施例。

圖 8 繪示包含一識別標記之一半導體封裝之一實施例。

圖 9 繪示包含一識別標記之一半導體封裝之一實施例。

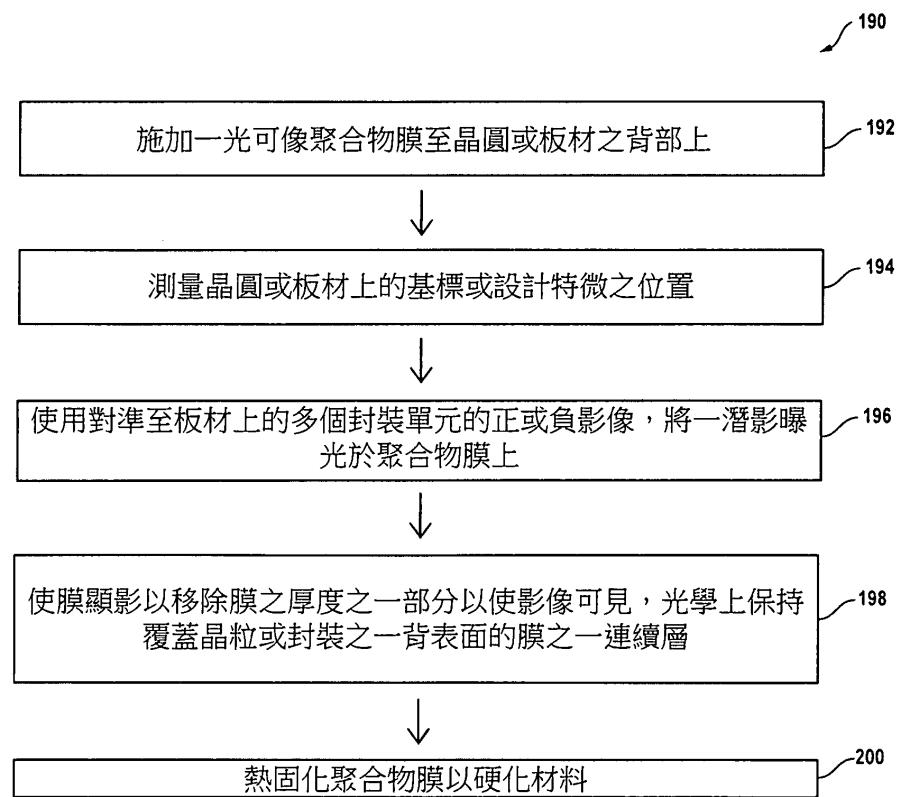

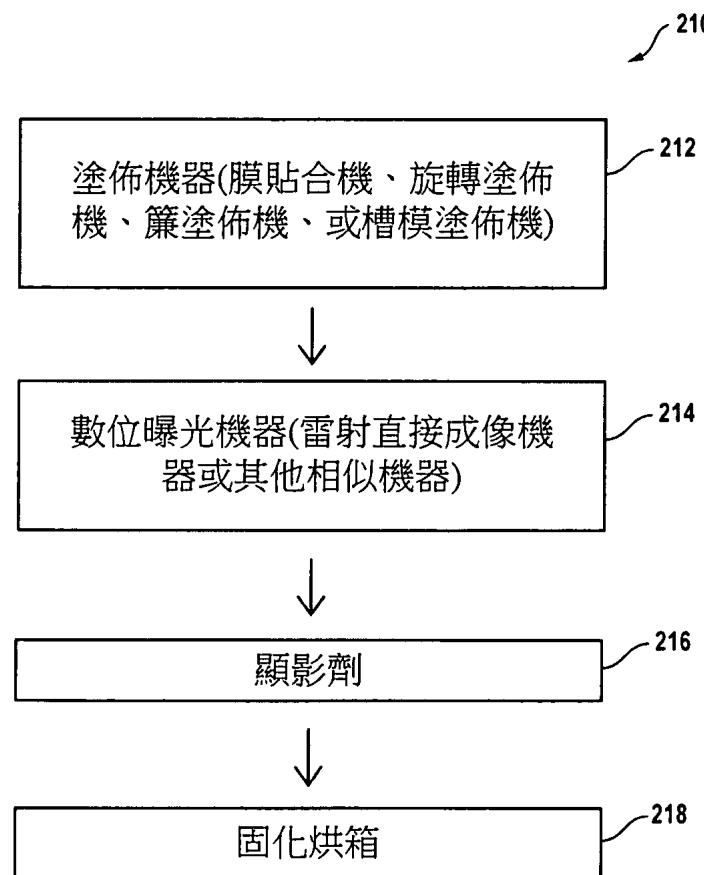

圖 10A 及圖 10B 繪示關於包含唯一識別符之半導體封裝之態樣之程式流程。

(3)

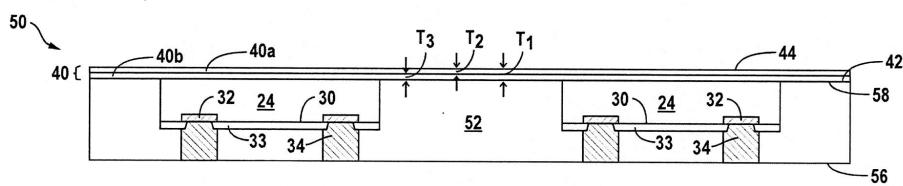

第 1 圖(先前技術)

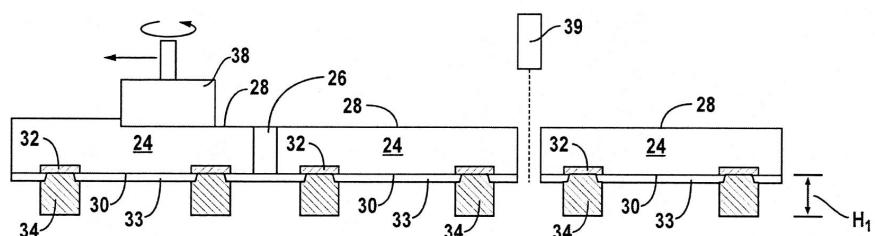

第 2A 圖

第 2B 圖

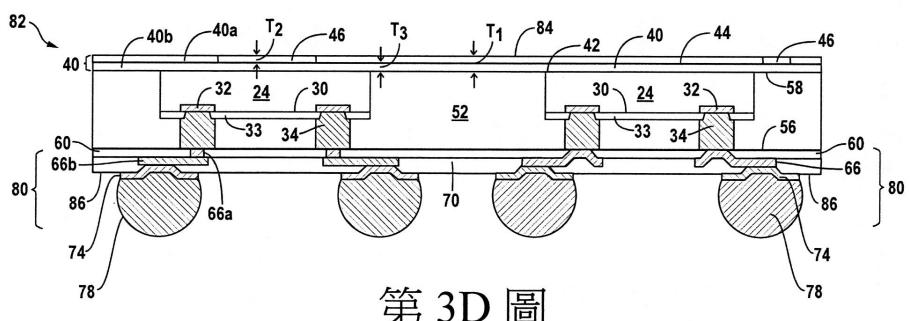

(4)

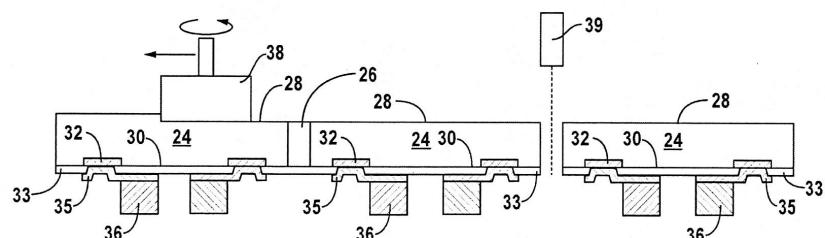

第 2C 圖

第 2D 圖

第 2E 圖

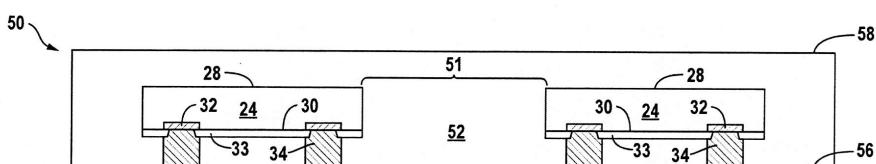

第 3A 圖

第 3B 圖

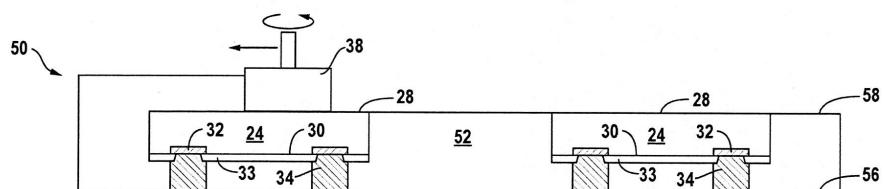

第 3C 圖

第 3D 圖

第 3E 圖

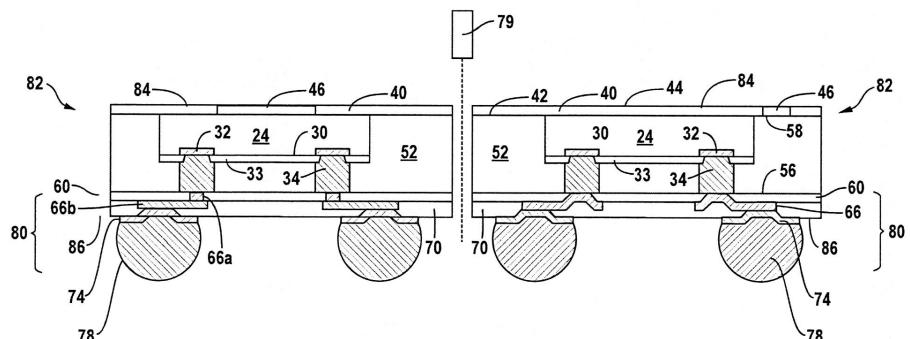

(6)

第 3F 圖

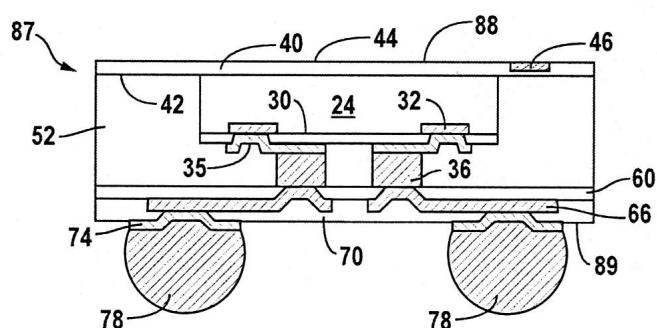

第 4 圖

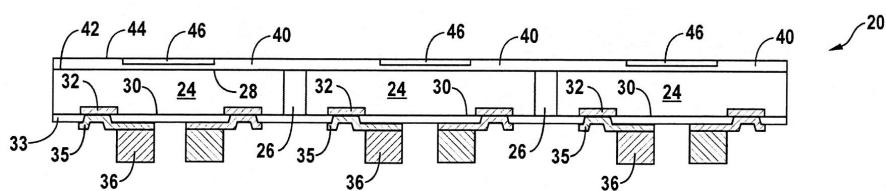

第 5 圖

(7)

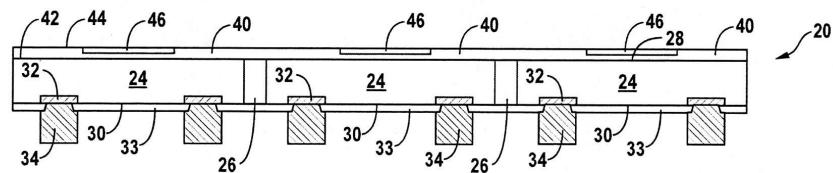

第6圖

第7圖

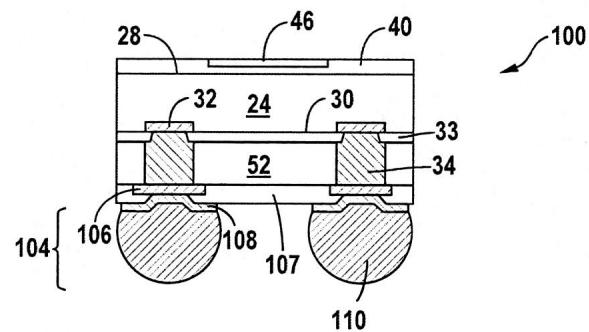

第8圖

第9圖

第 10A 圖

第 10B 圖