【11】證書號數：I664703

【45】公告日：中華民國 108 (2019) 年 07 月 01 日

【51】Int. Cl. : H01L23/48 (2006.01) H01L21/56 (2006.01)

發明

全 5 頁

【54】名稱：具有記憶體封裝下之控制器之記憶體裝置及相關之系統及方法

MEMORY DEVICES WITH CONTROLLERS UNDER MEMORY

PACKAGES AND ASSOCIATED SYSTEMS AND METHODS

【21】申請案號：107120206 【22】申請日：中華民國 104 (2015) 年 11 月 20 日

【11】公開編號：201838116 【43】公開日期：中華民國 107 (2018) 年 10 月 16 日

【30】優先權：2014/11/21 美國 14/550,243

【72】發明人：倪勝錦 (SG) YE, SENG KIM ; 黃宏遠 (CN) NG, HONG WAN

【71】申請人：美商美光科技公司 MICRON TECHNOLOGY, INC.

美國

【74】代理人：陳長文

【56】參考文獻：

TW 201431013A

TW 201436167A

US 2013/0161788A1

US 2014/0097513A1

審查人員：唐之凱

## 【57】申請專利範圍

1. 一種製造一半導體封裝之方法，該方法包括：在一封裝基板上方配置一控制器；在該一封裝基板上方配置一第一半導體封裝，使得該控制器定位於該第一半導體封裝與該封裝基板之間；在該第一半導體封裝上方配置一第二半導體封裝；及以一囊封劑囊封該第一半導體封裝及該第二半導體封裝及該控制器。

2. 如請求項 1 之方法，其進一步包括：將該控制器線接合至該封裝基板；及將該第一半導體封裝及該第二半導體封裝線接合至該封裝基板。

3. 如請求項 1 之方法，其進一步包括：使該囊封劑流動至該封裝基板與該第一半導體封裝之間之一空腔中，使得該囊封劑至少部分囊封該控制器。

4. 如請求項 1 之方法，其中在該封裝基板上方配置該第一半導體封裝包含：將該第一半導體封裝附著至該封裝基板，使得該控制器之大部分直接定位於該第一半導體封裝與該封裝基板之間。

5. 如請求項 1 之方法，其中在該封裝基板上方配置該第一半導體封裝包含：將該第一半導體封裝安裝至該封裝基板，使得耦合該控制器至該封裝基板之接線直接位於該第一半導體封裝與該封裝基板之間。

## 圖式簡單說明

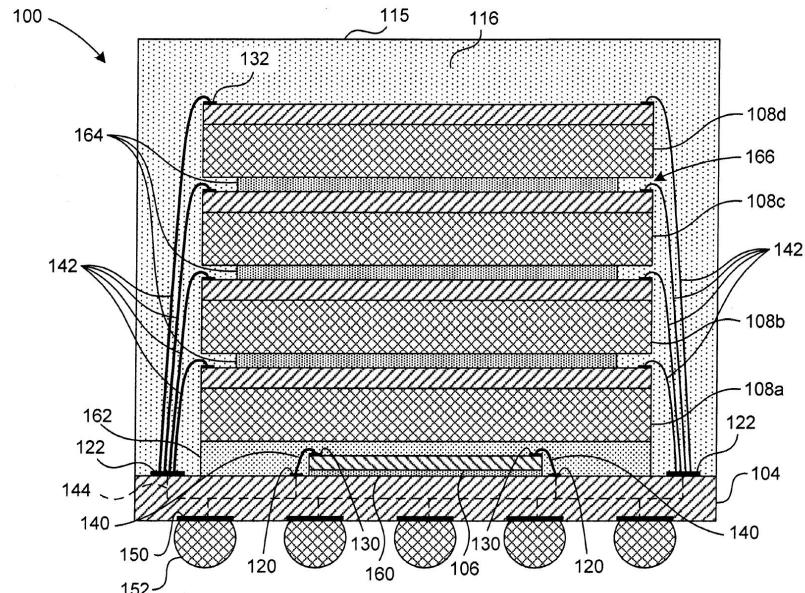

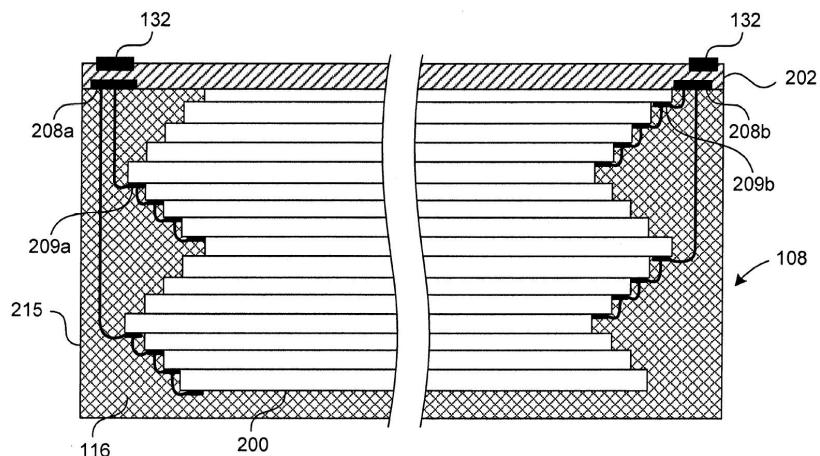

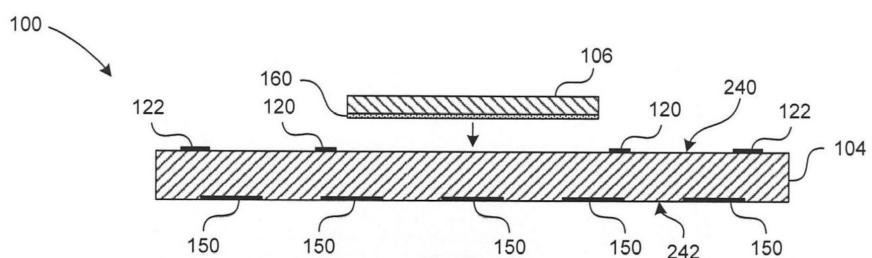

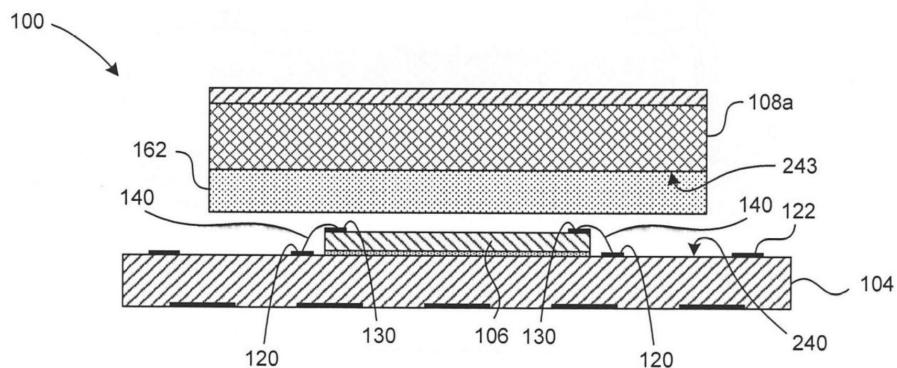

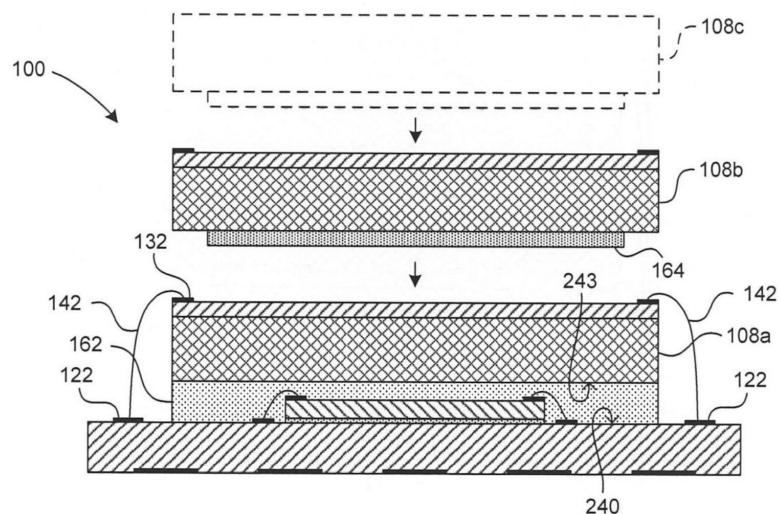

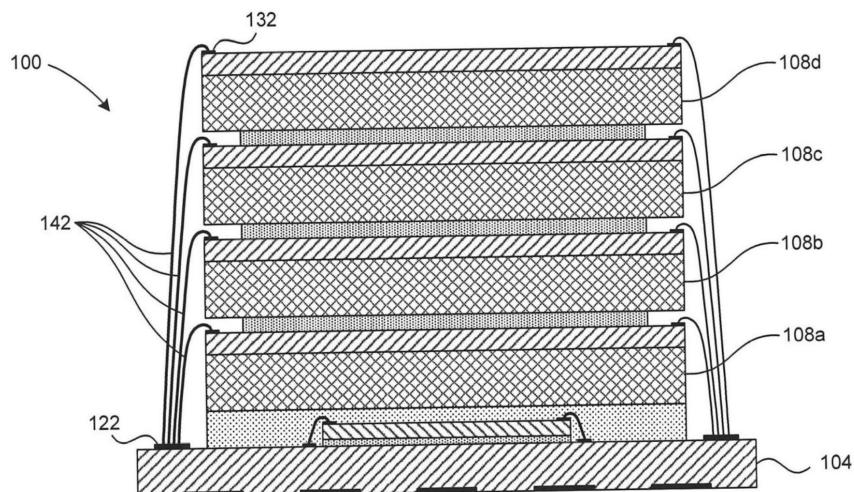

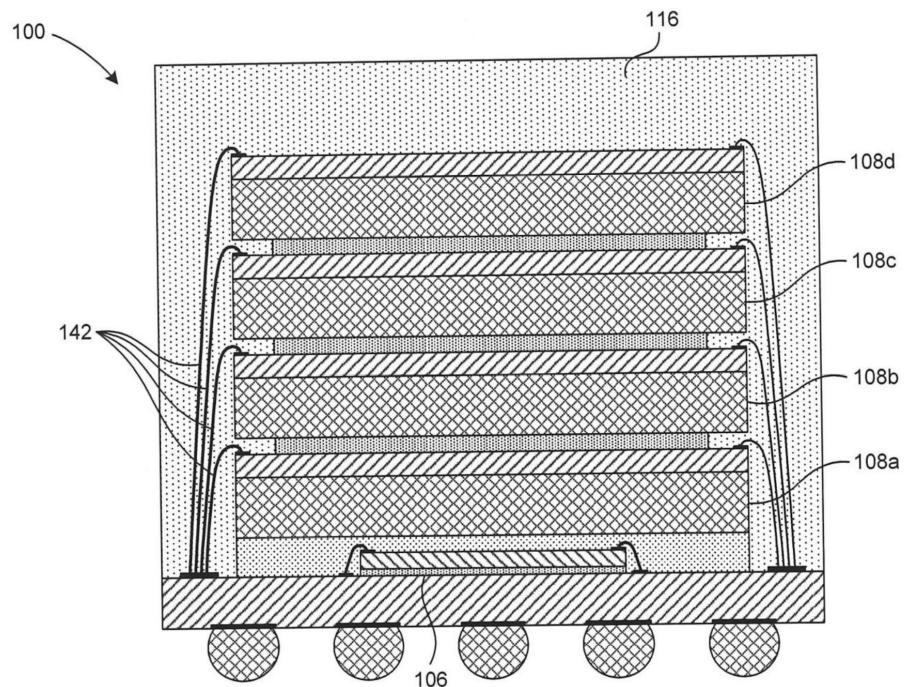

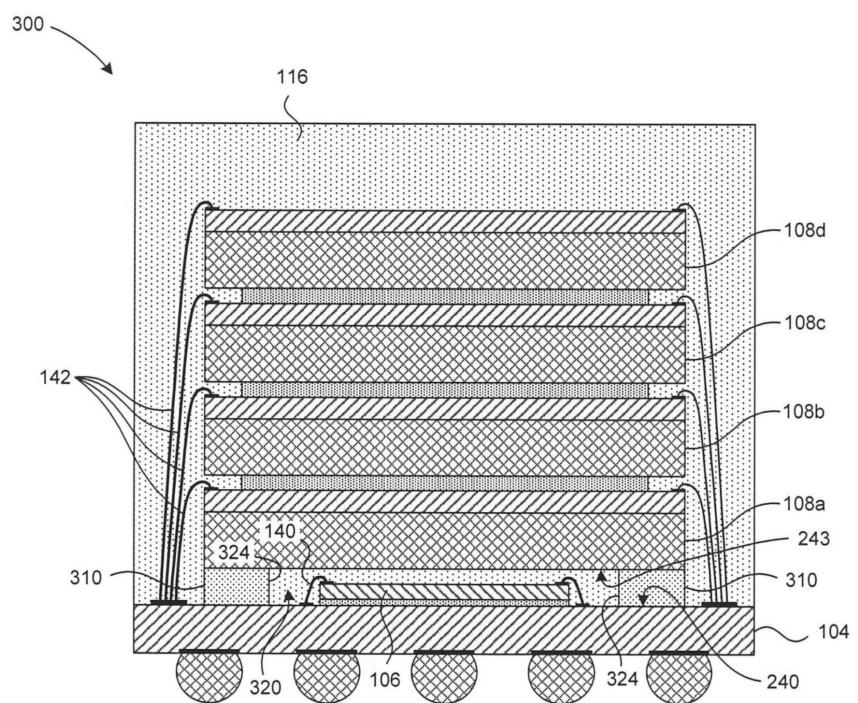

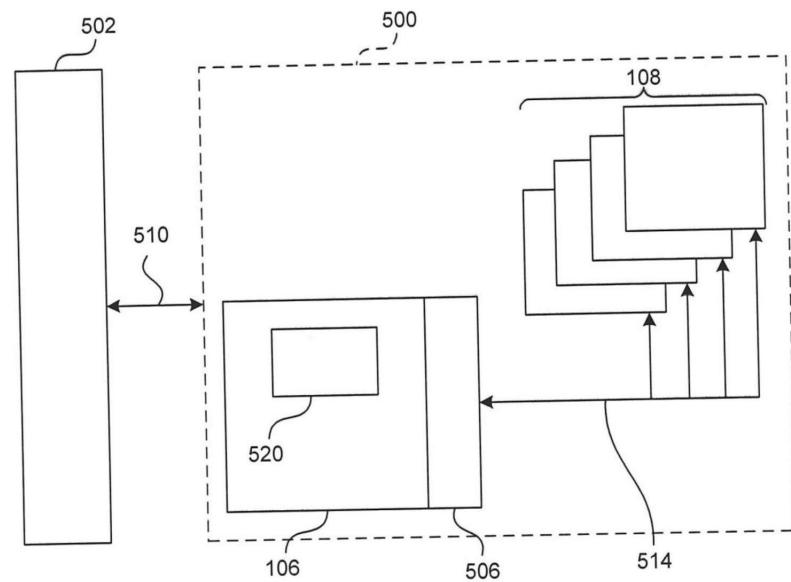

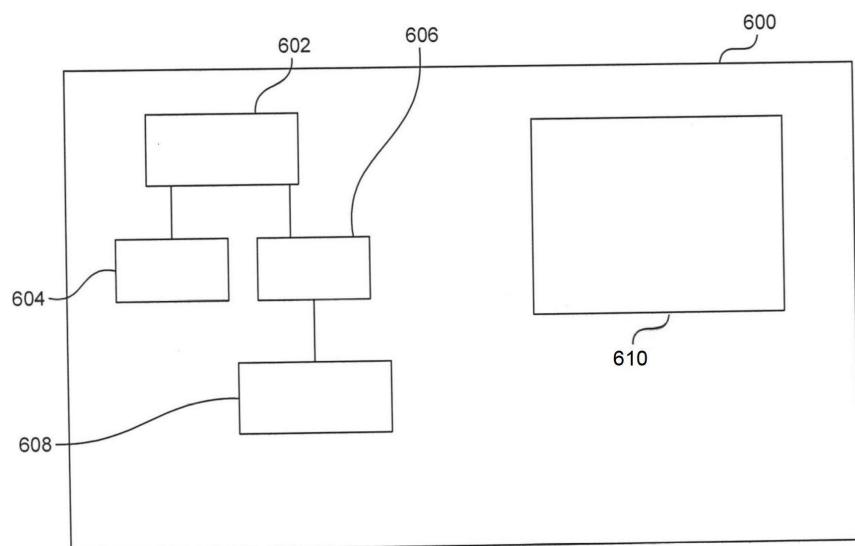

圖 1 係根據本發明之一實施例而組態之一記憶體裝置之一橫截面圖。圖 2 係根據本發明之一實施例而組態之一多晶粒記憶體封裝之一橫截面圖。圖 3A 至圖 3E 係繪示根據本發明之一實施例之各種製造階段中之一記憶體裝置的橫截面圖。圖 4 係根據本發明之另一實施例而組態之一記憶體裝置之一橫截面圖。圖 5 係繪示根據本發明之一實施例之適合用於記憶體裝置之一實施方案的一方塊電路圖。圖 6 係包含根據本發明之實施例而組態之一記憶體裝置的一系統之一示意圖。

(2)

【圖1】

〔圖2〕

【圖3A】

(3)

【圖3B】

【圖3C】

【圖3D】

(4)

【圖3E】

【圖4】

(5)

【圖5】

【圖6】