【11】證書號數：I663781

【45】公告日：中華民國 108 (2019) 年 06 月 21 日

【51】Int. Cl. : *H01Q1/40 (2006.01)*      *H01Q1/12 (2006.01)*

*H01Q21/00 (2006.01)*

發明

全 4 頁

【54】名稱：多頻天線封裝結構

【21】申請案號：106145791      【22】申請日：中華民國 106 (2017) 年 12 月 26 日

【72】發明人：管延城 (TW) KUAN, YEN CHENG ; 梁嘉仁 (TW) LIANG, CHIA JEN ; 蔣靜雯 (TW) CHIANG, CHING WEN ; 余建德 (TW) YU, CHIEN TE

【71】申請人：國家中山科學研究院      NATIONAL CHUNG-SHAN INSTITUTE

OF SCIENCE AND TECHNOLOGY

桃園市龍潭區中正路佳安段 481 號

【56】參考文獻：

|    |           |    |            |

|----|-----------|----|------------|

| TW | I521794   | TW | 201725693A |

| US | 9431369B2 | US | 9711465B2  |

| US | 9741690B1 |    |            |

審查人員：林宥榆

【57】申請專利範圍

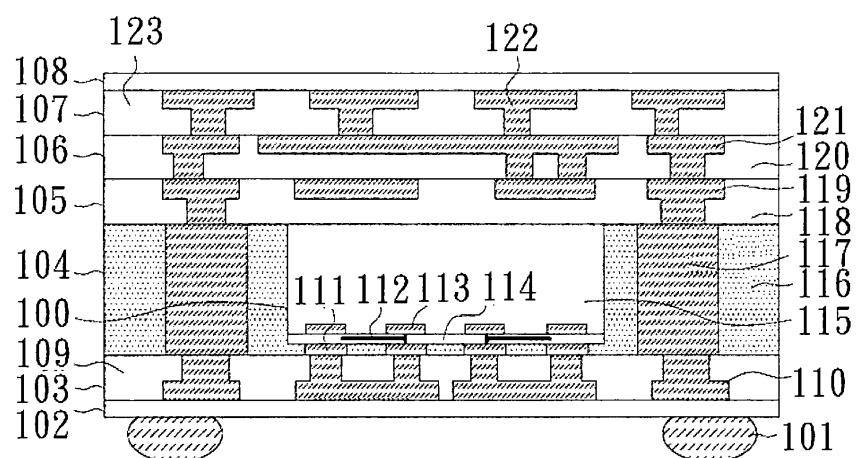

1. 一種多頻天線封裝結構，該結構係包括：一第一重佈線層，係包括一具有複數開口的第一介電材料層，及設置於該第一介電材料層的複數開口中的複數第一金屬層；一積體電路層，係設置於該第一重佈線層上，該積體電路層包括至少一金屬通孔(via)、至少一金屬柱(pillar)、一積體電路晶片和一模製(molding)層，其中該模製層用以填充於該金屬通孔形成的複數開口內，該金屬柱以及該積體電路晶片設置在該第一重佈線層上，該金屬通孔電連接該等第一金屬層的其中一者，該金屬柱電連接該積體電路晶片與該等第一金屬層的其中一者；一第二重佈線層，形成在該積體電路層上，該第二重佈線層包括一第二介電材料層和形成在該第二介電材料層的多個開口中的多個第二金屬層，其中該金屬通孔電連接該等第二金屬層中的其中一者；以及一第一天線單元層，包括一第一介電層和形成在該第一介電層的複數開口中的複數第三金屬層，其中該等第三金屬層中的至少一者電連接該等第二金屬層的其中一者，並且該等第三金屬層形成一第一天線單元，其中該第一天線單元為一多輸入多輸出相位天線，且該積體電路晶片的高度相同於或小於該金屬通孔的高度。

2. 如申請專利範圍第 1 項所述之多頻天線封裝結構，其中，該積體電路晶片係包括位於該積體電路晶片之一積體電路上的一第二天線單元。

3. 如申請專利範圍第 1 項所述之多頻天線封裝結構，更包括：一第一屏蔽層，形成於該第一天線單元層與該第二重佈線層之間，該第一屏蔽層包括形一第一介電層與成於該第二介質層的多個開口中的多個第四金屬層，其中該等第四金屬層電連接該等第三金屬層與部分的該等第二金屬層。

4. 如申請專利範圍第 3 項所述之多頻天線封裝結構，更包括：一第一保護層，其中該第一重佈線層設置於該第一保護層上；一第二保護層，形成在該第一天線單元層上；以及多個凸塊球(bump balls)，其中該多頻天線封裝結構透過過該等凸塊球安裝在一基板上。

5. 如申請專利範圍第 1 項所述之多頻天線封裝結構，更包括：一第二天線單元層，包括一第二介電層和形成在該第二介電層的多個開口中的多個第四金屬層，其中該等第四金屬

- 層中的至少一者電連接到該等第一金屬層中的其中一者，該等第四金屬層形成該第二天線單元，且該第一重佈線層形成在該第二天線單元層上。

6. 如申請專利範圍第 5 項所述之多頻天線封裝結構，更包括：一第一屏蔽層，形成於該第一天線單元層與該第二重佈線層之間，該第一屏蔽層包括一第三介電層與形成於該第三介電層的多個開口中的多個第五金屬層，其中該等第五金屬層電連接該等第三金屬層與部分的該等第二金屬層；以及一第二屏蔽層，形成於該第二天線單元層與該第一重佈線層之間，該第二屏蔽層包括一第四介電層與形成於該第四介質層的多個開口中的多個第六金屬層，該等第六金屬層電連接該等第四金屬層與部分的該等第一金屬層。

7. 如申請專利範圍第 6 項所述之多頻天線封裝結構，更包括：一第一保護層，其中該第一重佈線層位於該第一保護層上；一第二保護層，形成在該第一天線單元層上；以及多個凸塊球，其中該多頻天線封裝結構透過該等凸塊球安裝在一基板上。

8. 如申請專利範圍第 5 項所述之多頻天線封裝結構，其中，該第二天線單元為一多輸入多輸出相位天線。

9. 一種多頻天線封裝結構的製造方法，係包括：提供具有一第一膠層的第一臨時基板；在該第一膠層上形成一第一介電材料層，以及在該第一介電材料層的多個開口中形成多個第一金屬圖案；在該等第一金屬圖案的其中一者上形成至少一金屬通孔；在部分的該等第一金屬圖案的上形成至少一金屬柱，以及在該金屬柱上設置一積體電路晶片；形成一模製層以覆蓋該金屬柱、該金屬通孔與該積體電路晶片；薄化(thinning down)該模製層以暴露該金屬通孔，以形成包括該模製層、該金屬通孔、該金屬柱和該積體電路晶片的一積體電路晶片層；在該積體電路晶片層上形成一第一重佈線層，其中該第一重佈線層包括一第二介電材料層和多個第二金屬圖案，其中該等第二圖案形成在該第二介電材料層的多個開口中；在該第一重佈線層上形成一第一天線單元層，其中該第一天線單元層包括一第一介電層和形成在該第一介電層的多個開口中的多個第三金屬圖案，其中該等第三金屬圖案中的至少一個電連接該等第二金屬圖案的其中一者，且該等第三金屬圖案形成一第一天線單元；在該第一天線單元層上形成一第一保護層，以形成一第一堆疊結構；移除具有該第一膠層的該第一臨時基板，並且翻轉該第一堆疊結構以將該第一堆疊結構粘附到具有一第二膠層的第二臨時基板上；通過處理該第一介電材料層和該等第一金屬圖案來形成一第二重佈線層，其中該第二重佈線層包括經處理的該第一介電材料層和經處理的該等第一金屬圖案；在該第二重佈線層上形成一第二保護層；在該第二保護層上形成多個凸塊球，從而形成一第二堆疊結構；以及移除具有該第二膠層的該第二臨時基板，翻轉該第二堆疊結構，以通過該等凸塊球將該第二堆疊結構安裝在一基板上；其中該第一天線單元為一多輸入多輸出相位天線，且該積體電路晶片的高度相同於或小於該金屬通孔的高度。

10. 如請求項第 9 項所述之多頻天線封裝結構的製造方法，其中該積體電路晶片包括位於該積體電路晶片之一積體電路上的一第二天線單元。

11. 如請求項第 10 項所述之多頻天線封裝結構的製造方法，更包括：在形成該第一天線單元層之前，在該第一重佈線層上形成一第一屏蔽層，該第一屏蔽層包括一第二介質層和形成於該第二介質層的多個開口中的多個第四金屬圖案，該等第四金屬圖案電性連接該等第三金屬圖案和部分的該等第二金屬圖案。

12. 如請求項第 9 項所述之多頻天線封裝結構的製造方法，更包括：在形成該第二保護層之前，在該第二重佈線層上形成一第二天線單元層，其中該第二天線單元層包括一第二介質層和形成在該第二介質層的多個開口中的多個第四金屬圖案，其中該等第四金屬圖案電連接該等第一金屬圖案的其中一者，且該等第四金屬圖案形成一第二天線單元。

13. 如請求項第 12 項所述之多頻天線封裝結構的製造方法，更包括：在形成該第一天線單元層之前，在該第一重佈線層上形成一第一屏蔽層，該第一屏蔽層包括一第三介質層和形成於該第三介質層的多個開口中的多個第五金屬圖案，該等第五金屬圖案電性連接該等第三金屬圖案和部分的該等第二金屬圖案的；以及在該第二天線單元層形成之前，在該第二重佈線層上形成一第二屏蔽層，該第二屏蔽層包括一第四介質層和形成於該第四介質層的多個開口中的多個第六金屬圖案，該等第六金屬圖案電性連接該等第四金屬圖案和部分的該等第一金屬圖案。

14. 一種通訊裝置，包括：一多頻天線封裝結構，包括：一第一重佈線層，包括一第一介電材料層和形成在該第一介電材料層的多個開口中的多個第一金屬圖案；一積體電路層，形成於該第一重佈線層上，該積體電路層包括至少一金屬通孔、至少一金屬柱、一積體電路晶片和一模製層，其中該模製層用以填充該金屬通孔形成的多個開口，該金屬柱以及該積體電路晶片設置在該第一重佈線層上，該金屬通孔電連接該等第一金屬圖案的其中一者，該金屬柱電連接該積體電路芯片與該等第一金屬圖案的其中一者；一第二重佈線層，形成在該積體電路層上，該第二重佈線層包括一第二介電材料層和形成在該第二介電材料層的多個開口中的多個第二金屬圖案，其中該金屬通孔電連接該等第二金屬圖案中的其中一者；以及一第一天線單元層，包括一第一介電層和形成在該第一介電層的多個開口中的多個第三金屬圖案，其中該等第三金屬圖案中的至少一者電連接該等第二金屬圖案的其中一者，並且該等第三金屬圖案形成一第一天線單元；其中該積體電路晶片具有作為一處理電路的一積體電路，且該積體電路晶片具有位於該積體電路上的一第二天線單元，或者該該積體電路晶片不包括有該第二天線單元，但該多頻天線封裝結構更包括：一第二天線單元層，包括一第二介電層和形成在該第二介電層的多個開口中的多個第四金屬圖案，其中該等第四金屬圖案中的至少一者電連接到該等第一金屬圖案中的其中一者，該等第四金屬圖案形成該第二天線單元，且該第一重佈線層形成在該第二天線單元層上；其中該第一天線單元為一多輸入多輸出相位天線，且該積體電路晶片的高度相同於或小於該金屬通孔的高度。

15. 如請求項第 14 項所述之通訊裝置，其中該通訊裝置係為一加密通訊裝置或一頻率轉換裝置。

**圖式簡單說明**

第 1 圖係為本發明多頻天線封裝結構示意圖。

第1圖