【11】證書號數：I663702

【45】公告日：中華民國 108 (2019) 年 06 月 21 日

【51】Int. Cl. : H01L23/58 (2006.01)

H01L23/60 (2006.01)

發明

全 7 頁

## 【54】名稱：半導體封裝組件

A SEMICONDUCTOR PACKAGE ASSEMBLY

【21】申請案號：107113706 【22】申請日：中華民國 107 (2018) 年 04 月 23 日

【11】公開編號：201917866 【43】公開日期：中華民國 108 (2019) 年 05 月 01 日

【30】優先權：2017/10/26 美國 15/794,128

【72】發明人：孫瑞伯 (TW) SUN, RUEY BO ; 林聖謀 (TW) LIN, SHENG MOU ; 吳文洲 (TW) WU, WEN CHOU

【71】申請人：聯發科技股份有限公司

新竹市新竹科學工業園區篤行一路 1 號

【74】代理人：洪澄文；顏錦順

## 【56】參考文獻：

TW 201606997A TW 201717540A

TW 201729388A

審查人員：邱迺軒

## 【57】申請專利範圍

- 一種半導體封裝組件，其中包括：基板，具有晶粒附接表面和與晶粒附接表面相對的焊球附接表面；半導體晶粒，安裝在該基板的晶粒附接表面上，其中該半導體晶粒包括：射頻電路；以及電連接到該射頻電路的第一晶粒焊盤；基座，安裝在該基板的焊球附接表面上；以及第一電感器結構，在該基板、該半導體晶粒或該基座上，其中該第一電感器結構包括：電連接到該第一晶粒焊盤的第一端子；以及電連接到接地端子的第二端子；其中從該第一電感器結構的第二端子到該第一晶粒焊盤的第一導電路徑的第一距離小於從該半導體封裝組件的天線到該第一晶粒焊盤的第二導電路徑的第二距離。

- 如申請專利範圍第 1 項所述之半導體封裝組件，其中從該第一電感器結構的第一端子至該第一晶粒焊盤的第三導電路徑的第三距離小於該第二導電路徑沿著該基板佈置的區段的長度的 1/5。

- 如申請專利範圍第 2 所述之半導體封裝組件，其中從該第一電感器結構的第一端子至該第一晶粒焊盤的第三導電路徑的第三距離小於該第二導電路徑沿著該基板佈置的區段的長度的 1/10。

- 如申請專利範圍第 1 所述之半導體封裝組件，其中該第一電感器結構的第一端子直接接觸該第一晶粒焊盤。

- 如申請專利範圍第 1 所述之半導體封裝組件，其中該第一電感器結構直接位於該半導體晶粒上，該第一電感器結構包括主動電感器結構。

- 如申請專利範圍第 5 所述之半導體封裝組件，其中該主動電感器結構包括經典的回轉器-C 主動電感器結構。

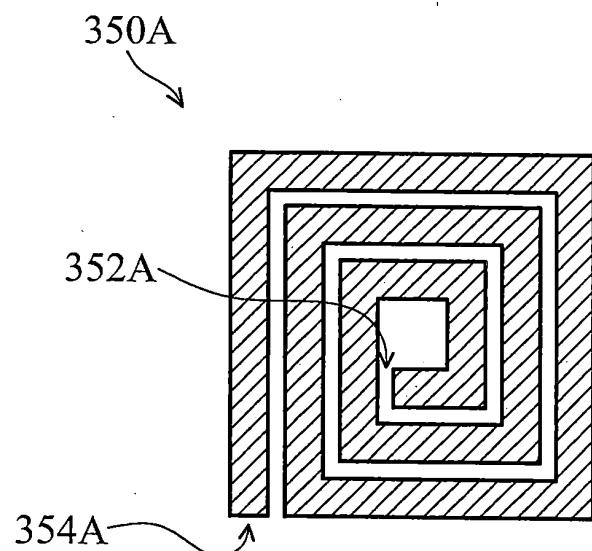

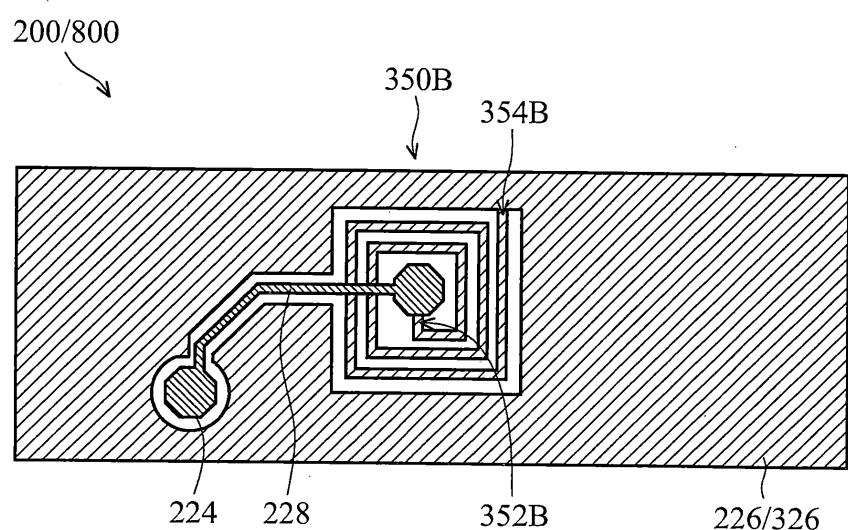

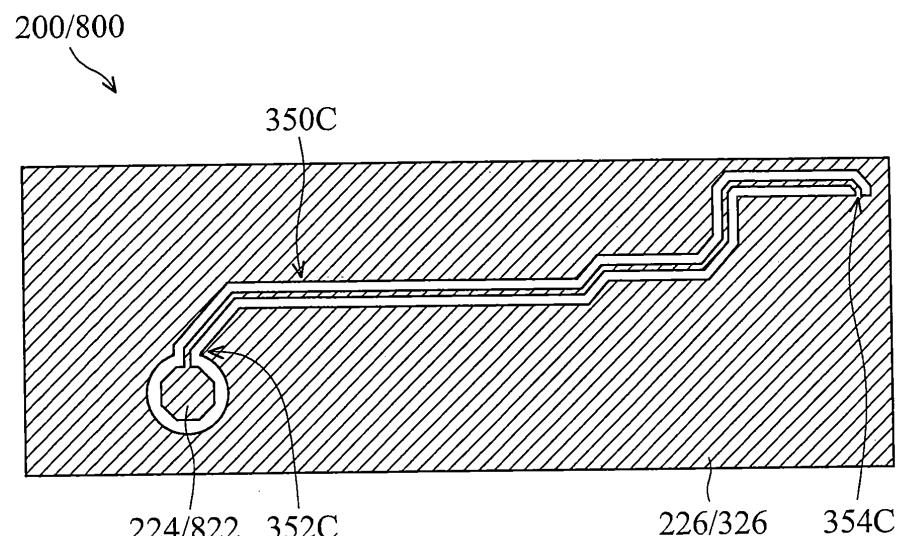

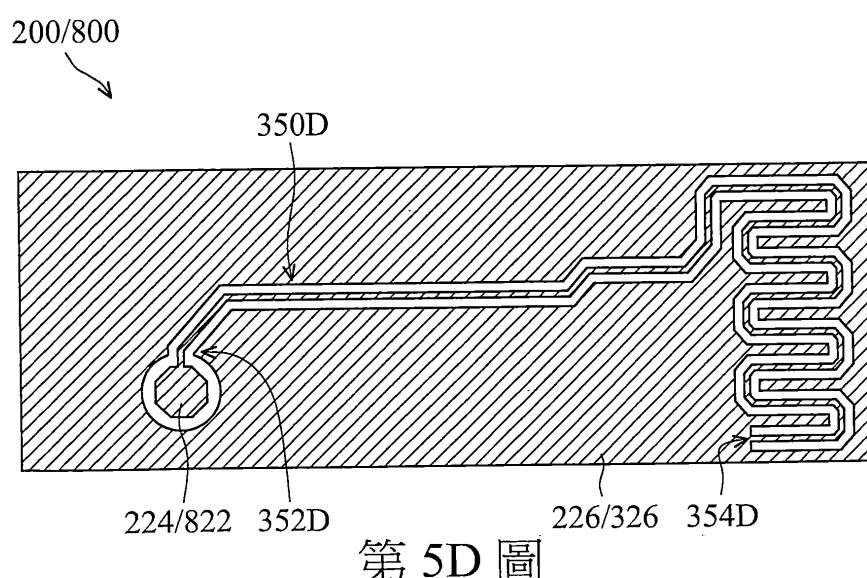

- 如申請專利範圍第 1 所述之半導體封裝組件，其中該第一電感器結構包括被動電感器結構，該被動電感器結構包括方形螺旋形電感器結構、短柱形電感器結構、曲折線形電感器結構或螺旋形電感器結構。

8. 如申請專利範圍第 1 所述之半導體封裝組件，其中該第一電感器結構包括六角形螺旋電感器結構、八角形螺旋電感器結構、圓形螺旋電感器結構、整合被動器件、表面安裝器件或接合線。

9. 如申請專利範圍第 1 所述之半導體封裝組件，其中，該基板包括：第一焊盤，在該基板的晶粒附接表面上；導電佈線，靠近該基板的晶粒附接表面且電連接到該第一焊盤；通孔結構，穿過該基板並電連接到該導電佈線的；以及其中該基座包括：第二焊盤，在該焊球附接表面上，其中第二焊盤電連接到該通孔結構和該第一電感器結構的第一端子，其中直接位於該基座上的該第一電感器結構、該第一焊盤、該導電佈線、該通孔結構及該第二焊盤共同形成複合電感器結構。

10. 如申請專利範圍第 1 所述之半導體封裝組件，其中該第一電感器結構與該半導體晶粒、該基板或該基座接觸。

11. 如申請專利範圍第 1 所述之半導體封裝組件，其中該半導體晶粒包括：第二晶粒焊盤，其中該第二晶粒焊盤電連接到該半導體晶粒的射頻電路和基座上的天線，其中該第一晶粒焊盤將該第一電感器結構與該第二晶粒焊盤分離。

12. 如申請專利範圍第 1 所述之半導體封裝組件，其中還包括：晶粒外部件電路，與該半導體晶粒的射頻電路電連接，其中該晶粒外部件電路包括匹配電路、濾波器和天線。

13. 如申請專利範圍第 12 所述之半導體封裝組件，其中該匹配電路包括第二電感器結構，其中該第一電感器結構與該第二電感器結構為分離的電感器結構。

14. 如申請專利範圍第 1 所述之半導體封裝組件，其中該半導體晶粒包括：數位/類比電路；以及數位/類比晶粒焊盤，電連接到數位/類比電路。

15. 如申請專利範圍第 14 所述之半導體封裝組件，其中該第一晶粒焊盤和該數位/類比晶粒焊盤係分離的晶粒焊盤。

16. 一種半導體封裝組件，其中包括：半導體晶粒，安裝在基座上，其中該半導體晶粒包括：射頻電路；電連接到該射頻電路的第一晶粒焊盤；基板，在該半導體晶粒和該基座之間；以及第一電感器結構，在該基板、該半導體晶粒或該基座上，其中該第一電感器結構包括：電連接到該第一晶粒焊盤的第一端子；以及電連接到接地端子的第二端子；天線，在基座上，並且不經過該第一電感器結構而電連接到該第一晶粒焊盤。

17. 如申請專利範圍第 16 所述之半導體封裝組件，其中該射頻電路包括接收器或發射器。

18. 如申請專利範圍第 16 所述之半導體封裝組件，其中該半導體晶粒包括：第二晶粒焊盤，電連接到該射頻電路和該天線，其中該第一晶粒焊盤將該第一電感器結構與該第二晶粒焊盤分離。

19. 如申請專利範圍第 18 所述之半導體封裝組件，其中還包括：晶粒外部件電路，與該第二晶粒焊盤電連接，其中該晶粒外部件電路包括匹配電路、濾波器和天線。

20. 如申請專利範圍第 19 所述之半導體封裝組件，其中該匹配電路係該第二導電路徑的一部份，其中第二導電路徑從該天線到該第一晶粒焊盤。

21. 一種半導體封裝組件，其中包括：半導體晶粒，安裝在基座上，其中該半導體晶粒包括：射頻電路；電連接到該射頻電路的第一晶粒焊盤；基板，在該半導體晶粒和該基座之間；以及第一電感器結構，在該基板、該半導體晶粒或該基座上，其中該第一電感器結構包括：電連接到該第一晶粒焊盤的第一端子；以及電連接到接地端子的第二端子；天線，在基座上，並且電連接到該第一晶粒焊盤，其中從該第一電感器結構的第二端子到該第一晶粒焊盤的第一導電路徑的第一距離小於從該天線到該第一晶粒焊盤的第二導電路徑的第二距離，其中該第一晶粒焊盤在該第一導電路徑與該第二導電路徑之間。

圖式簡單說明

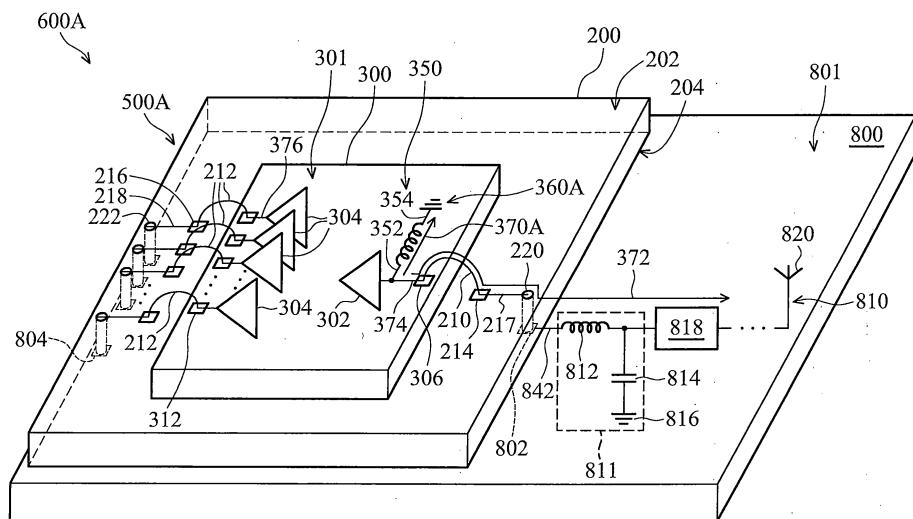

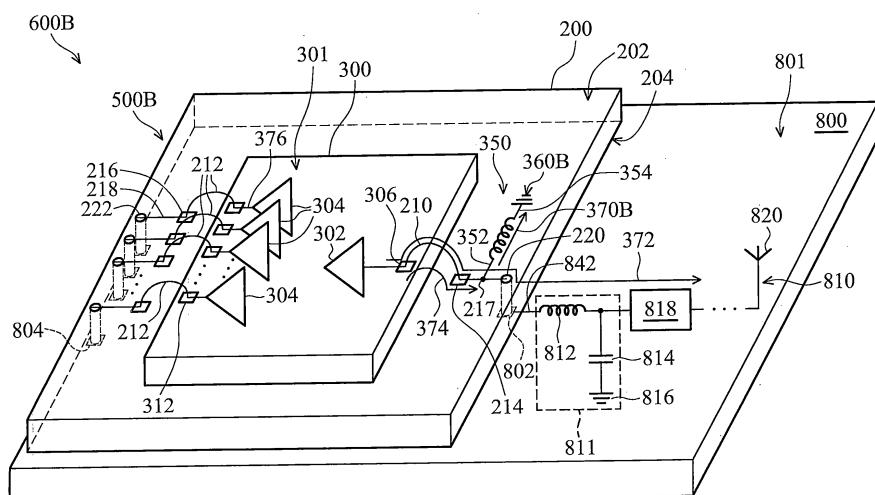

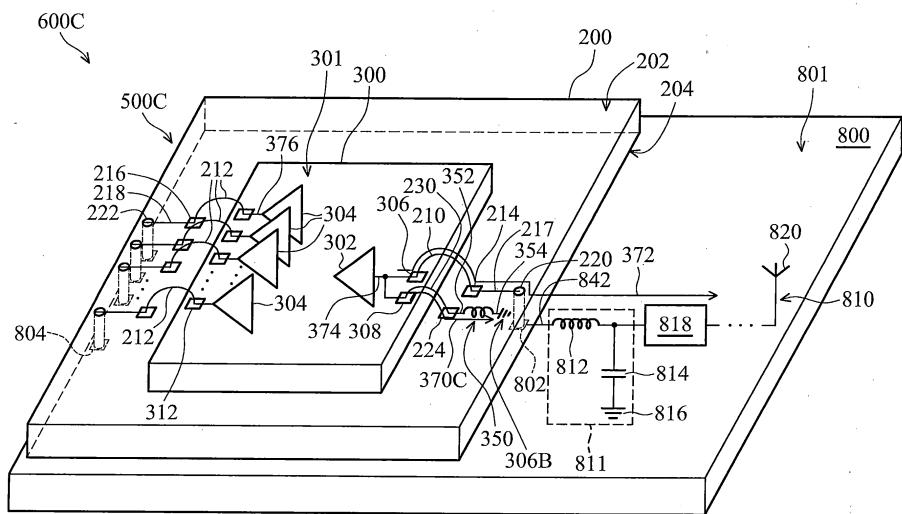

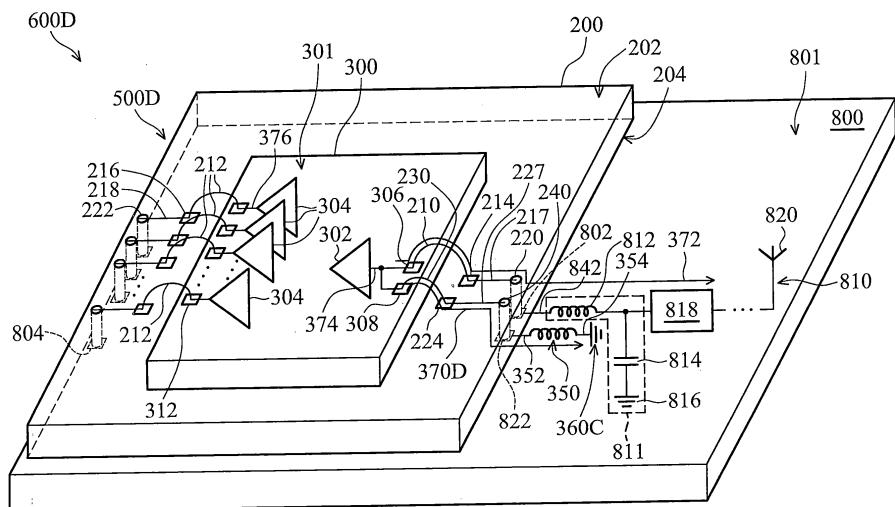

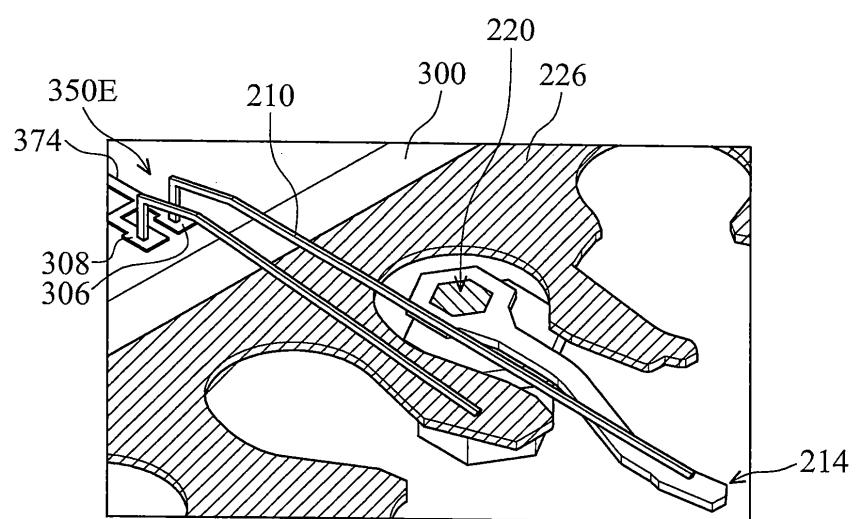

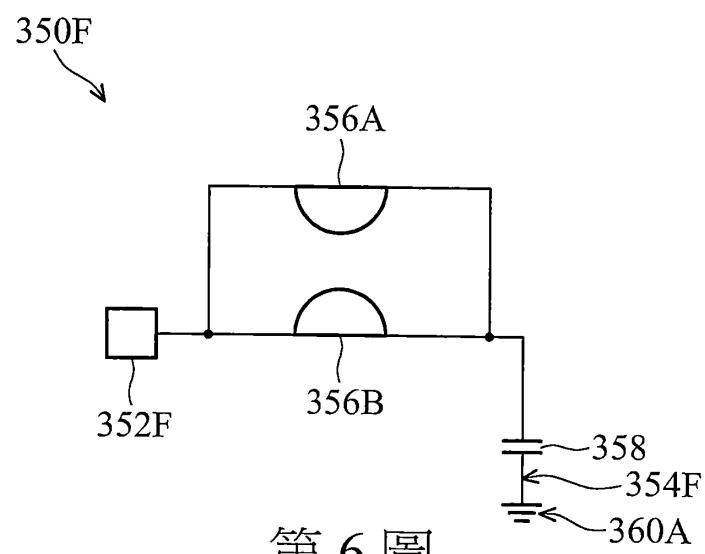

通過閱讀後續的詳細描述和實施例可以更全面地理解本發明，該實施例參照附圖給出，其中：第1-4圖係根據本發明的一些實施例的半導體封裝組件的電路圖；第5A-5E圖係根據本發明的一些實施例的位於半導體封裝組件上的同一封裝的被動電感器結構的俯視圖；第6圖係根據本發明的一些實施例的位於半導體封裝組件上的同一封裝的主動電感器結構的電路圖。

第1圖

第2圖

第3圖

#### 第4圖

(5)

第 5A 圖

第 5B 圖

(6)

第 5C 圖

第 5D 圖

第 5E 圖

第 6 圖