【11】證書號數：I662632

【45】公告日：中華民國 108 (2019) 年 06 月 11 日

【51】Int. Cl. : H01L21/60 (2006.01)

H01L23/52 (2006.01)

發明

全 15 頁

**【54】名稱：**形成支撐層於薄扇出晶圓級晶片尺寸封裝中之半導體晶粒之上的半導體裝置和方法

SEMICONDUCTOR DEVICE AND METHOD OF FORMING SUPPORTING LAYER OVER SEMICONDUCTOR DIE IN THIN FAN-OUT WAFER LEVEL CHIP SCALE PACKAGE

【21】申請案號：105139676

【22】申請日：中華民國 102 (2013) 年 08 月 02 日

【11】公開編號：201717296

【43】公開日期：中華民國 106 (2017) 年 05 月 16 日

【30】優先權：2012/09/28

美國

13/630,912

【72】發明人：林耀劍 (SG) LIN, YAOJIAN；陳康 (SG) CHEN, KANG；顧煜 (CN) GU, YU

【71】申請人：新加坡商史達晶片有限公司 STATS CHIPAC, LTD.

新加坡

【74】代理人：閻啟泰；林景郁

【56】參考文獻：

US 20100120204

US 20100120204A1

US 20110121449A1

審查人員：黃本立

**【57】申請專利範圍**

1. 一種製造半導體裝置的方法，其包括：提供一第一支撐層，其具有一開口在該第一支撐層中；置放一半導體晶粒在該第一支撐層的該開口之中，其中該開口的覆蓋區大於該半導體晶粒的覆蓋區；以及沉積一囊封劑於該半導體晶粒和該第一支撐層上方。

2. 根據申請專利範圍第 1 項的方法，其進一步包含形成一互連結結構於該半導體晶粒的主動表面和該囊封劑之一表面上方。

3. 根據申請專利範圍第 1 項的方法，其進一步包含：移除該囊封劑的一部分以曝露該半導體晶粒的背表面；以及形成一第二支撐層以接觸該半導體晶粒的該背表面以及在移除該囊封劑的該部分之後的該囊封劑的遺留部分。

4. 根據申請專利範圍第 1 項的方法，其中該第一支撐層包含一纖維增強型聚合物矩陣複合材料。

5. 根據申請專利範圍第 1 項的方法，其中該第一支撐層的高度是低於該半導體晶粒的高度。

6. 根據申請專利範圍第 1 項的方法，其進一步包含移除該囊封劑的一部分。

7. 一種製造半導體裝置的方法，其包括：提供一半導體晶粒；形成一第一支撐層於該半導體晶粒周圍的一周邊區域中；沉積一囊封劑於該半導體晶粒和該第一支撐層上方；形成一互連結結構於該半導體晶粒和該囊封劑之一第一表面上方；以及形成一第二支撐層於相對於該囊封劑之該第一表面的該囊封劑的一第二表面上方。

8. 根據申請專利範圍第 7 項的方法，其中該第二支撐層包含一聚合物介電膜。

9. 一種半導體裝置，其包括：一第一支撐層；一半導體晶粒，其被置放在該第一支撐層的一開口之中，其中一間隙存在於該開口中而在該半導體晶粒和該第一支撐層之間；以及一囊封劑，其被沉積於該半導體晶粒和該第一支撐層上方。

10. 根據申請專利範圍第 9 項的半導體裝置，其進一步包含被形成於該半導體晶粒和該囊封劑之一第一表面上方的一互連結構。

11. 根據申請專利範圍第 10 項的半導體裝置，其進一步包含被形成於相對於該囊封劑之該第一表面的該囊封劑的一第二表面上方的一第二支撐層。

12. 根據申請專利範圍第 11 項的半導體裝置，其中該第二支撐層包含一聚合物介電膜。

13. 根據申請專利範圍第 10 項的半導體裝置，其中該第一支撐層包含一纖維增強型聚合物矩陣複合材料。

#### 圖式簡單說明

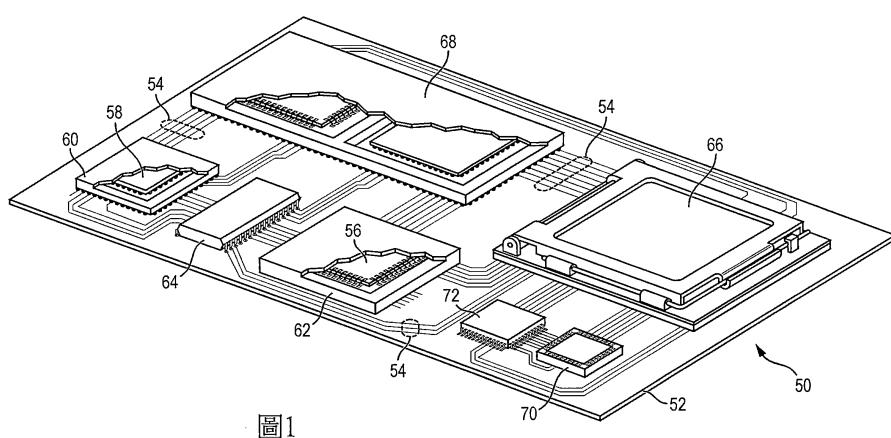

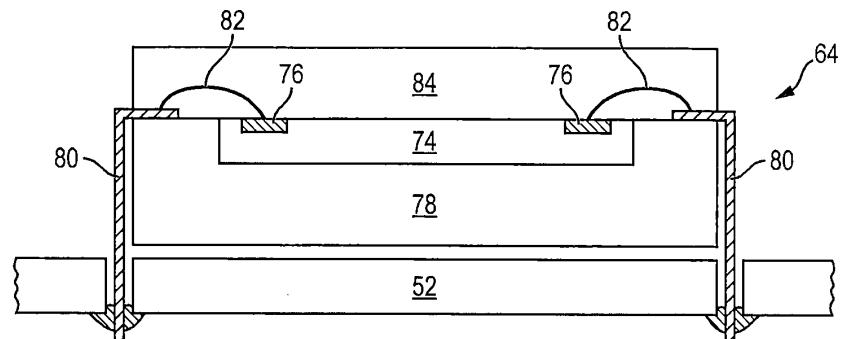

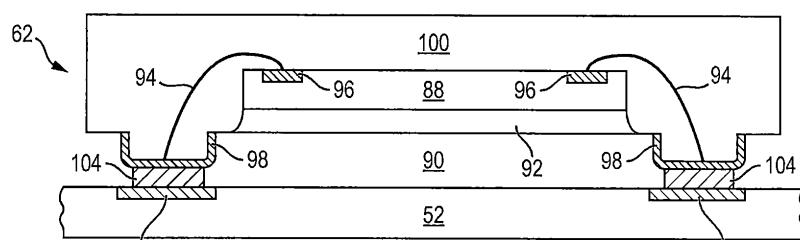

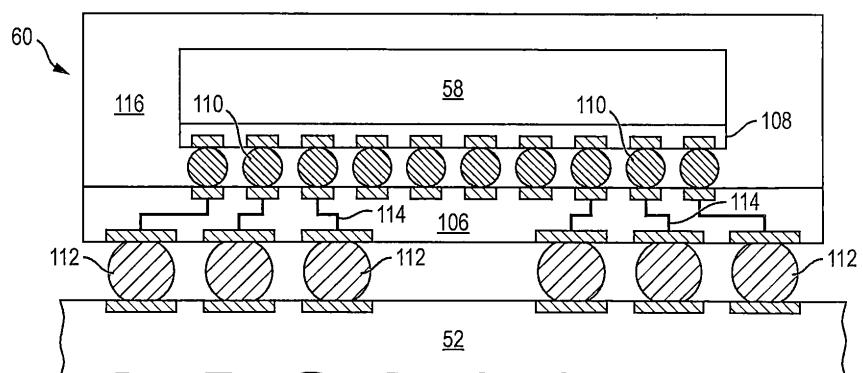

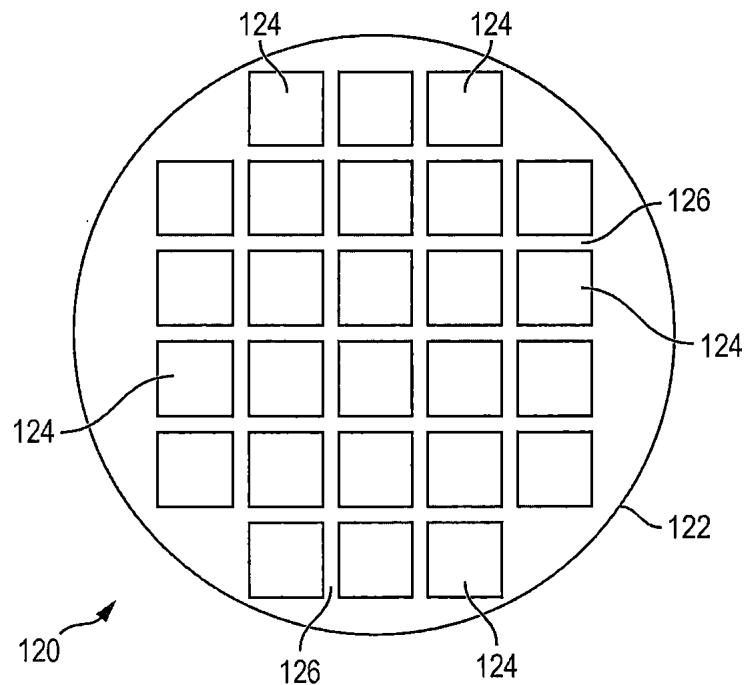

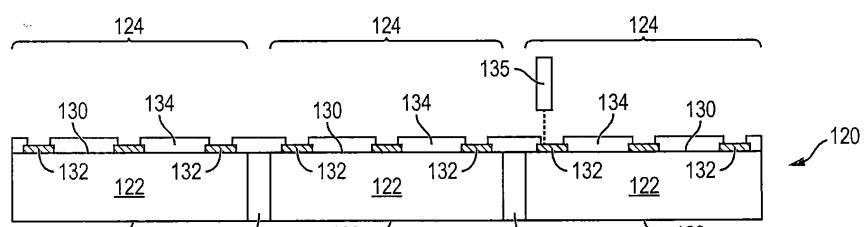

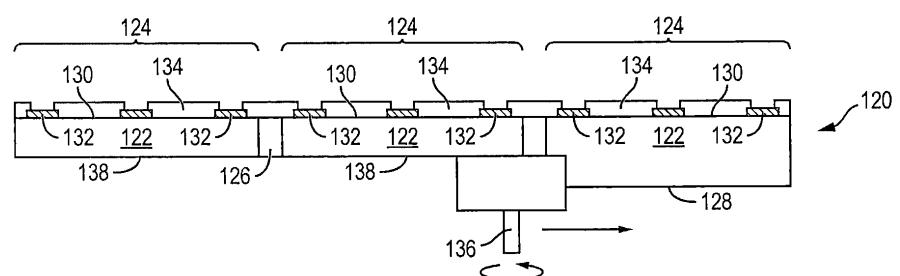

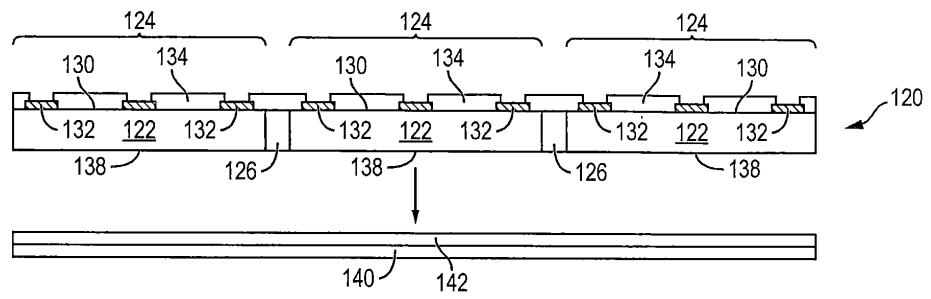

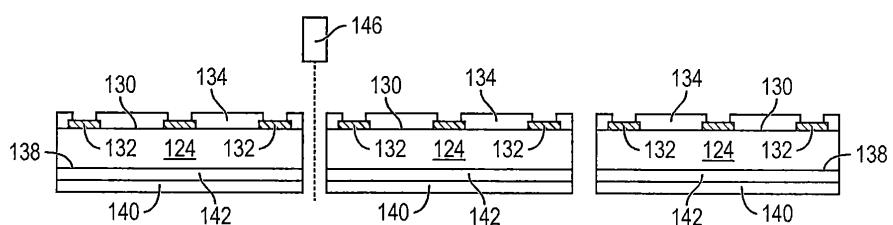

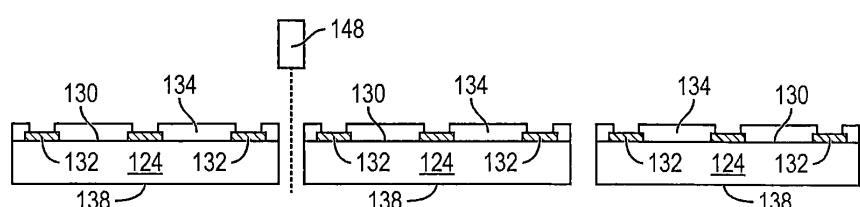

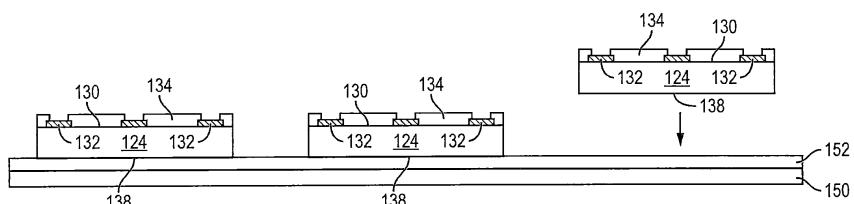

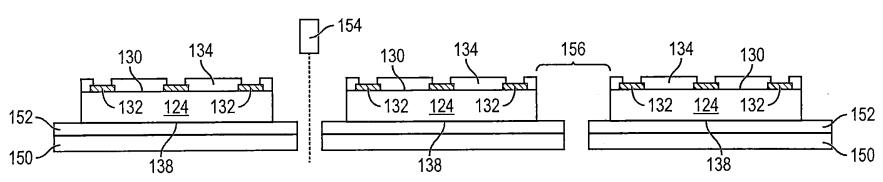

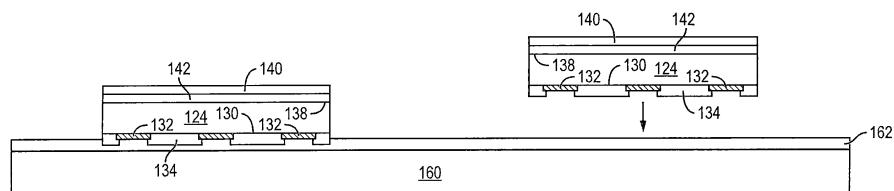

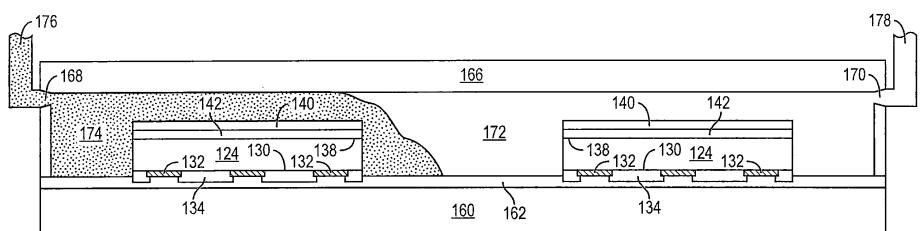

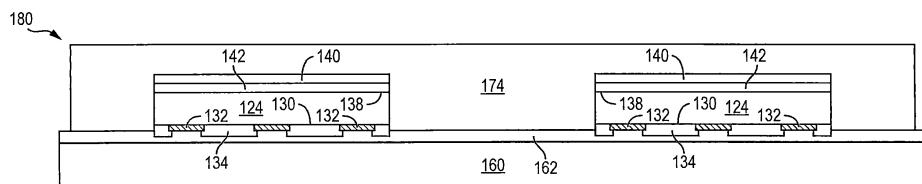

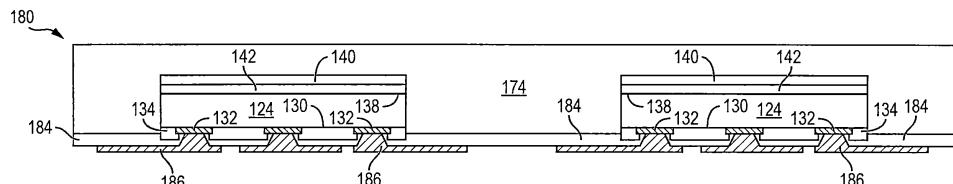

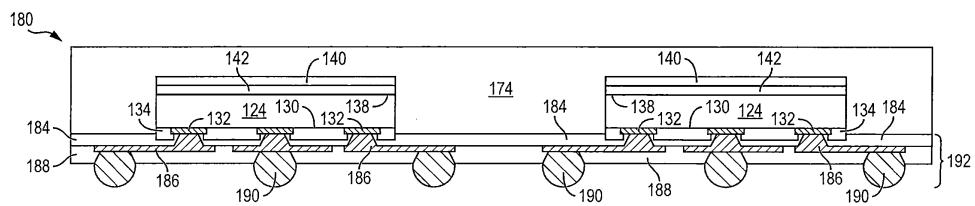

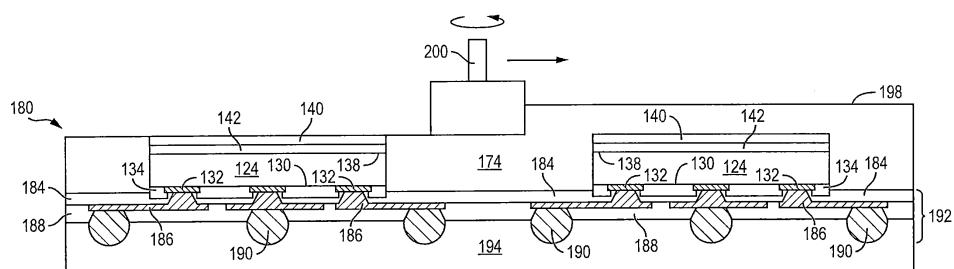

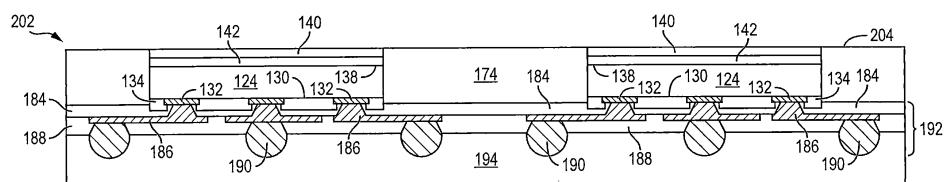

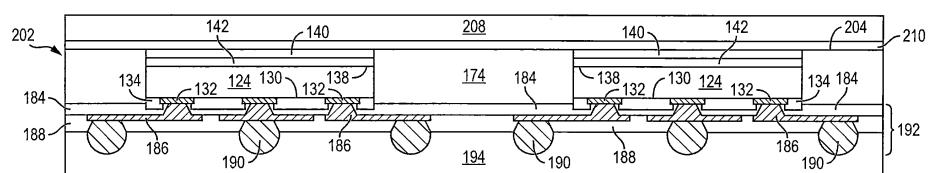

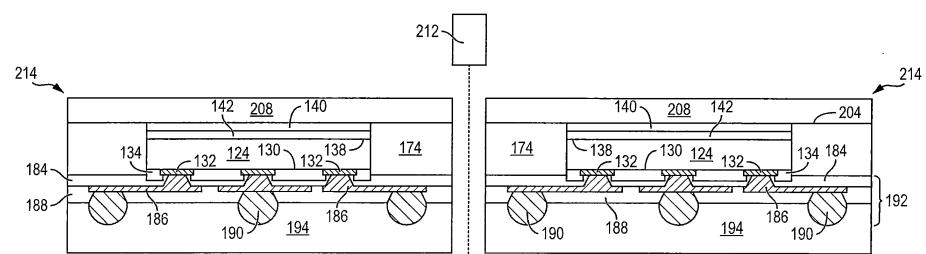

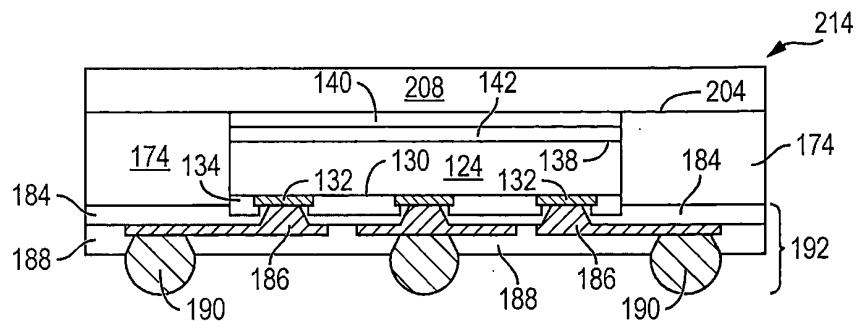

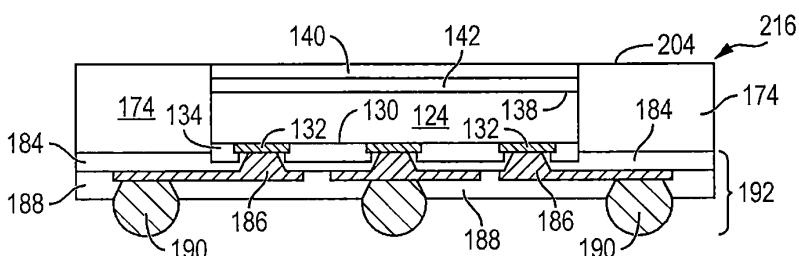

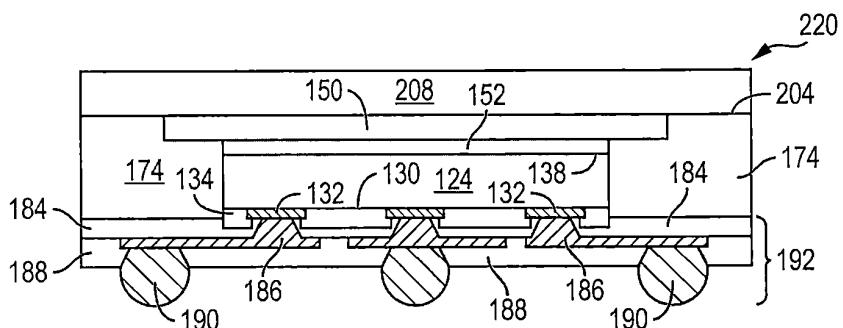

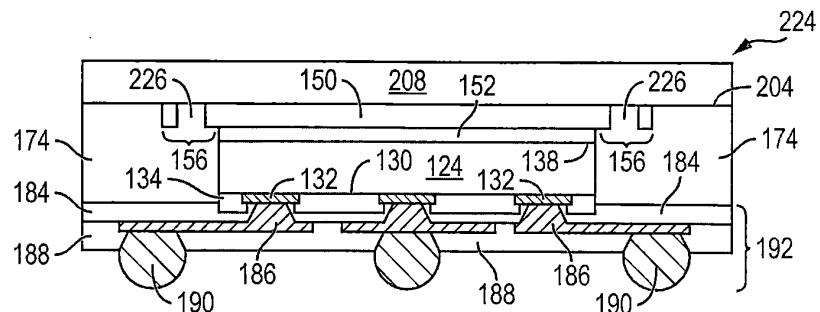

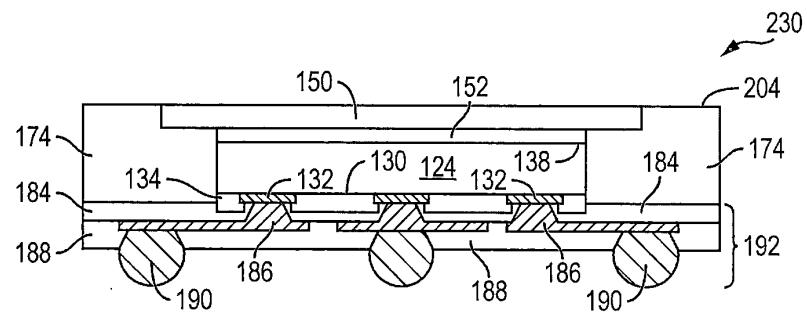

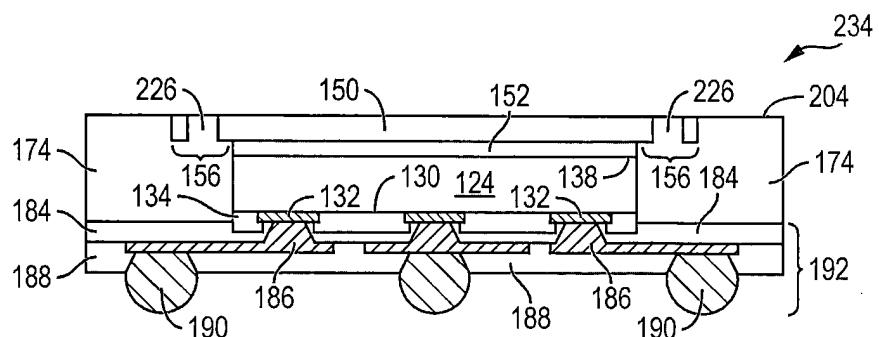

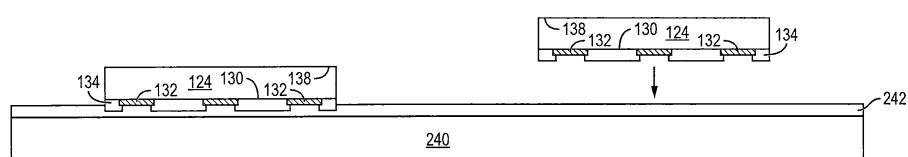

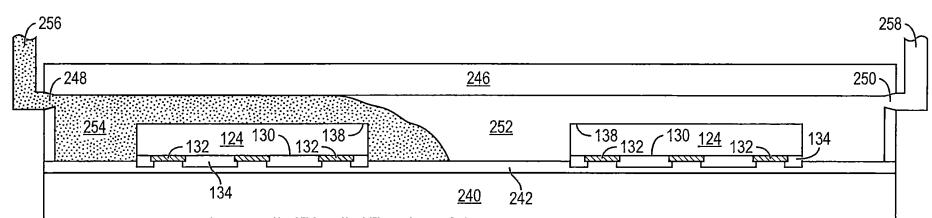

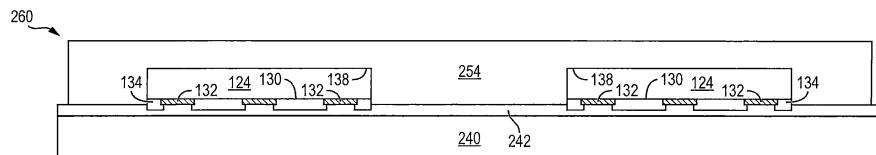

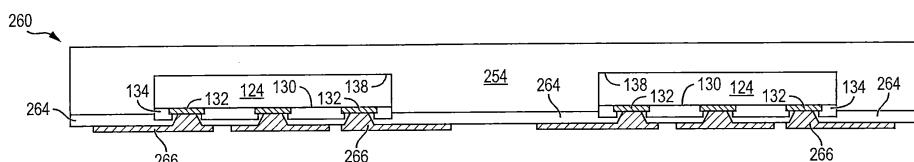

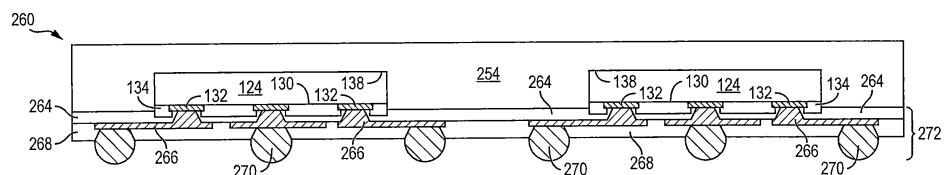

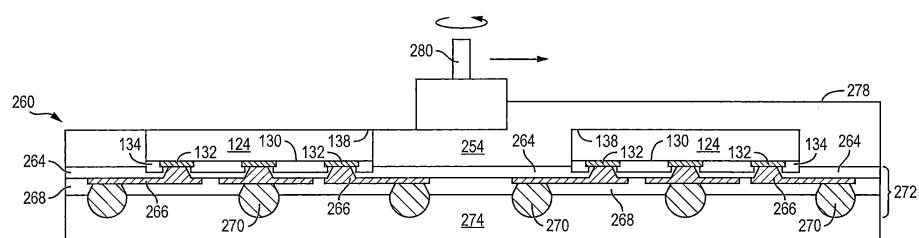

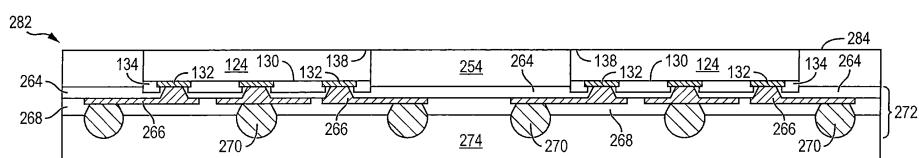

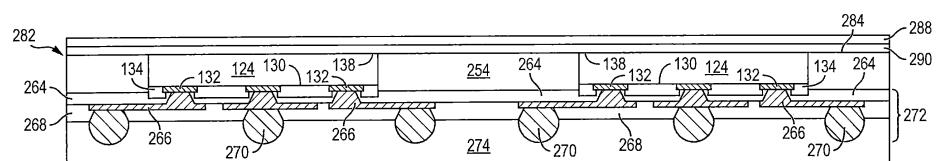

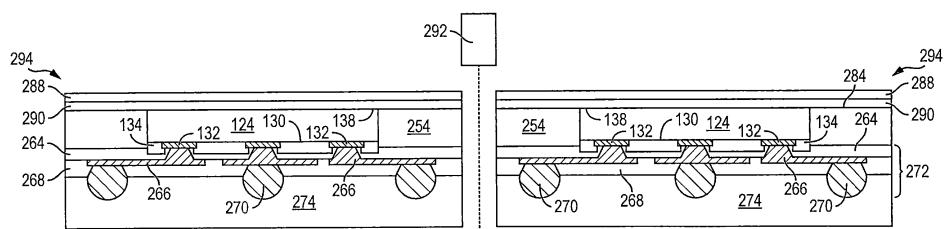

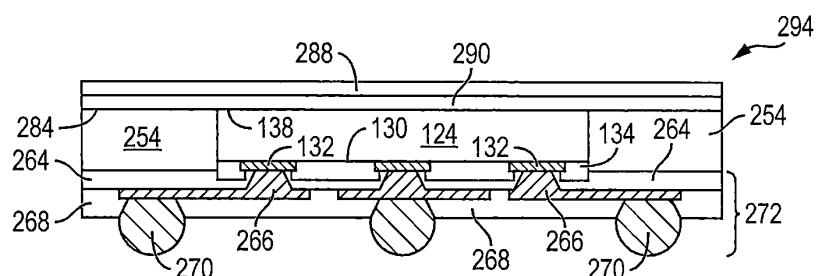

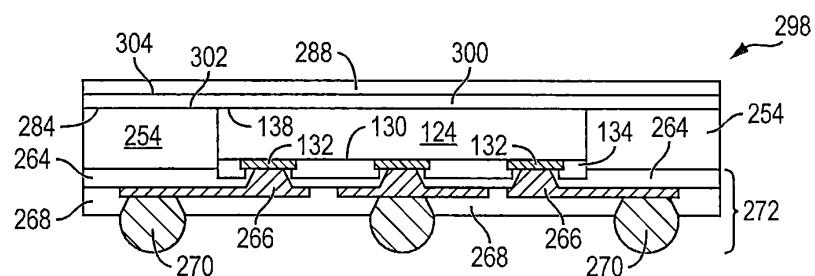

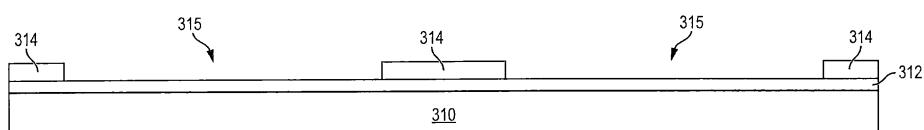

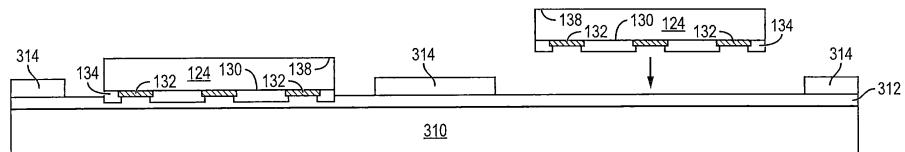

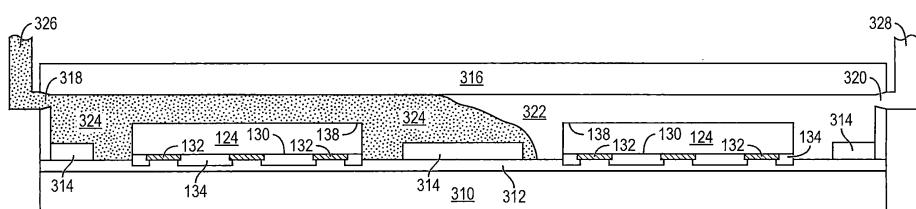

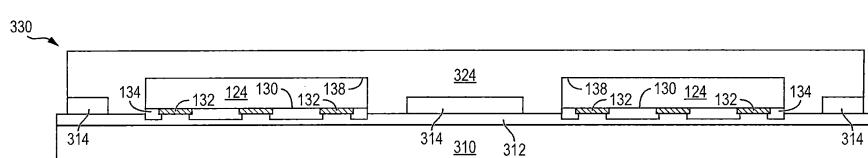

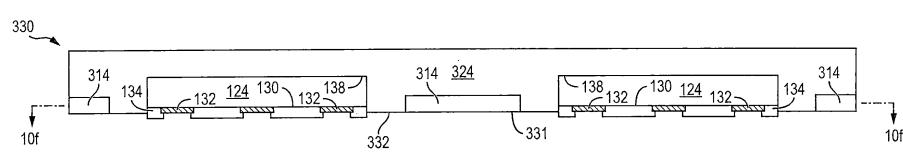

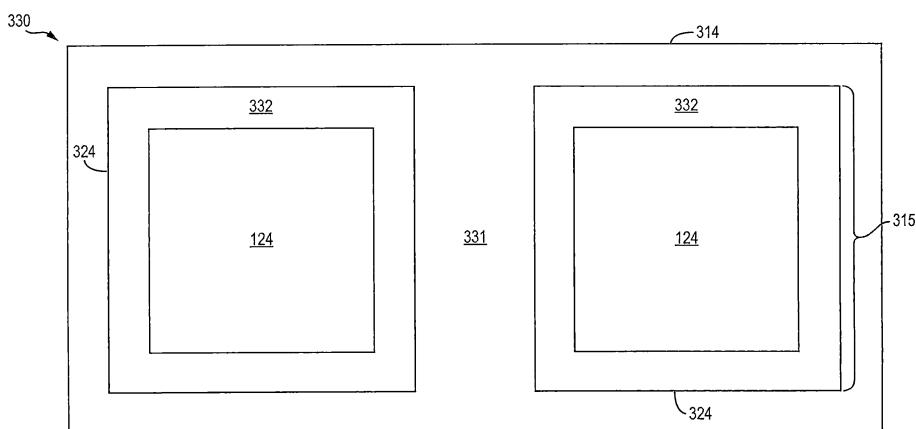

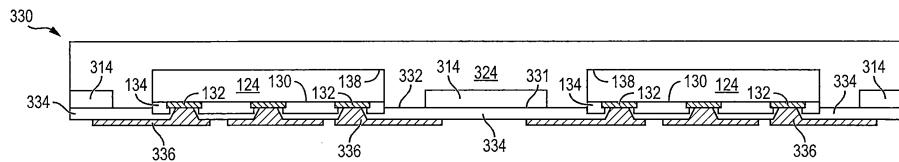

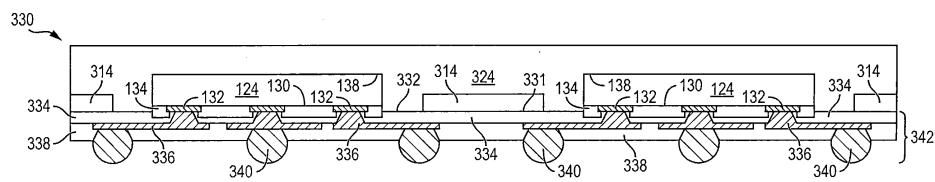

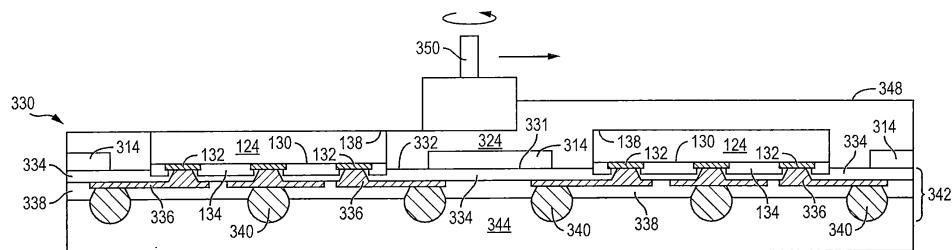

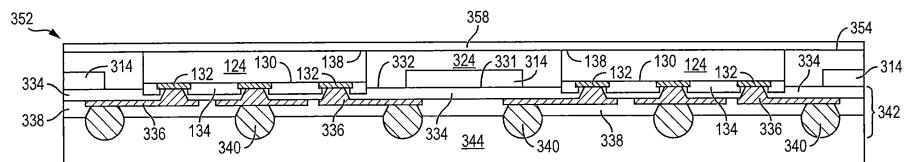

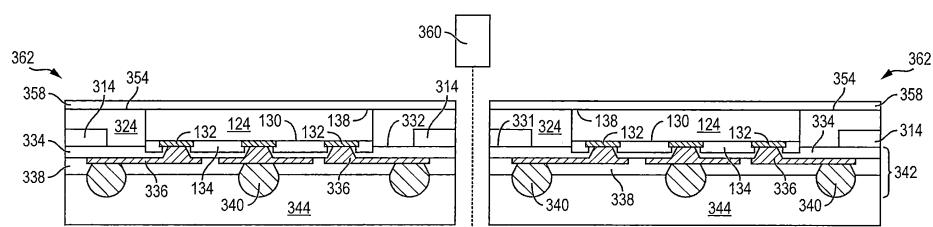

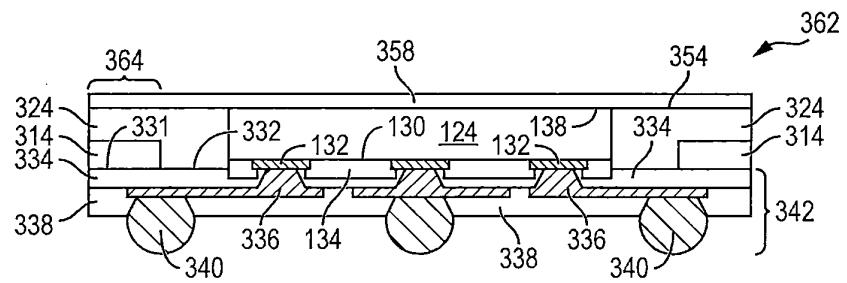

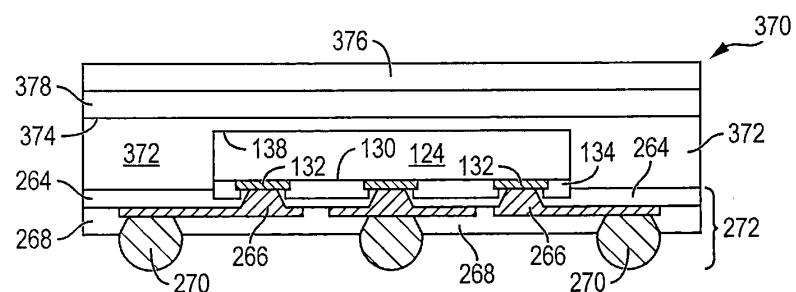

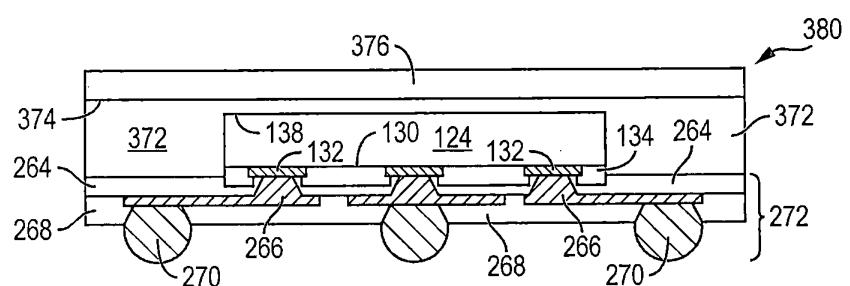

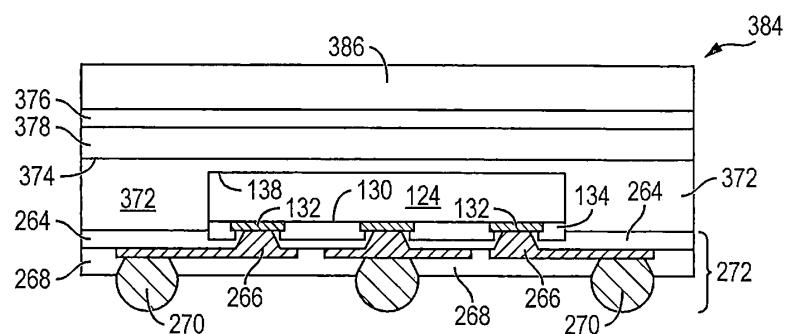

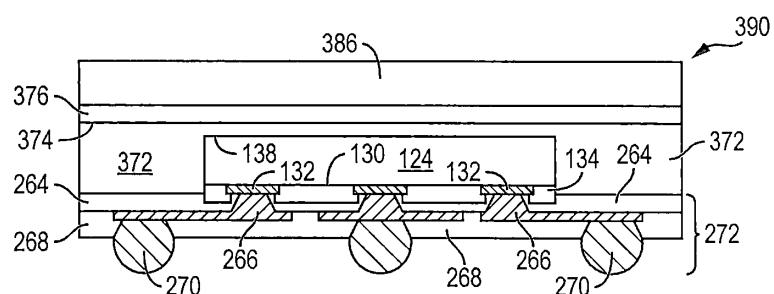

圖 1 所示的係一印刷電路板(PCB)，在其表面安裝著不同類型的封裝；圖 2a 至 2c 所示的係被安裝至該 PCB 的代表性半導體封裝的進一步細節；圖 3a 至 3h 所示的係藉由切割道分離之具有複數個半導體晶粒的半導體晶圓；圖 4a 至 4j 所示的係形成一支撐層於一薄扇出晶圓級晶片尺寸封裝中的半導體晶粒上方的製程；圖 5a 和 5b 所示的係形成於一薄扇出晶圓級晶片尺寸封裝中的半導體晶粒上方的一支撐層的實施例；圖 6a 至 6d 所示的係形成於一薄扇出晶圓級晶片尺寸封裝中的半導體晶粒上方的一支撐層的實施例；圖 7a 至 7j 所示的係形成一支撐層於一薄扇出晶圓級晶片尺寸封裝中的半導體晶粒上方的製程；圖 8 所示的係形成於一薄扇出晶圓級晶片尺寸封裝中的半導體晶粒上方的一支撐層的一個實施例；圖 9 所示的係形成於一薄扇出晶圓級晶片尺寸封裝中的半導體晶粒上方的一支撐層的另一個實施例；圖 10a 至 10k 所示的係形成一支撐層於一薄扇出晶圓級晶片尺寸封裝中的半導體晶粒上方的製程；圖 11 所示的係形成於一薄扇出晶圓級晶片尺寸封裝中的半導體晶粒上方的一支撐層的另一個實施例；圖 12a 和 12b 所示的係形成於一薄扇出晶圓級晶片尺寸封裝中的半導體晶粒上方的一支撐層的實施例；圖 13a 和 13b 所示的係形成於一薄扇出晶圓級晶片尺寸封裝中的半導體晶粒上方的一支撐層的實施例。

圖1

(3)

圖2a

圖2b

圖2c

(4)

圖3a

圖3b

圖3c

(5)

圖3d

圖3e

圖3f

圖3g

圖3h

(6)

圖4a

圖4b

圖4c

圖4d

圖4e

(7)

圖4f

圖4g

圖4h

圖4i

圖4j

圖5a

圖5b

圖6a

圖6b

(9)

圖6c

圖6d

圖7a

圖7b

圖7c

(10)

圖7d

圖7e

圖7f

圖7g

圖7h

圖7i

(11)

圖7j

圖8

圖9

圖10a

(12)

圖10b

圖10c

圖10d

圖10e

圖10f

(13)

圖10g

圖10h

圖10i

圖10j

圖10k

圖11

圖12a

圖12b

圖13a

圖13b