【11】證書號數：I662631

【45】公告日：中華民國 108 (2019) 年 06 月 11 日

【51】Int. Cl. : H01L21/60 (2006.01) H01L25/04 (2014.01)

發明

全 12 頁

【54】名稱：在扇出晶圓級晶片尺寸封裝上堆疊半導體晶粒之半導體裝置和方法

SEMICONDUCTOR DEVICE AND METHOD OF STACKING

SEMICONDUCTOR DIE ON A FAN-OUT WLCSP

【21】申請案號：103119637

【22】申請日：中華民國 103 (2014) 年 06 月 06 日

【11】公開編號：201501227

【43】公開日期：中華民國 104 (2015) 年 01 月 01 日

【30】優先權：2013/06/28

美國 61/841,059

2014/04/24 美國 14/261,252

【72】發明人：包旭升 (SG) BAO, XUSHENG；司徒 國強 (SG) SZETO, KWOKKEUNG

【71】申請人：新加坡商史達晶片有限公司 STATS CHIPPAC, LTD.

新加坡

【74】代理人：閻啟泰；林景郁

【56】參考文獻：

US 6847105B2 US 2004/0070064A1

US 2012/0012990A1 US 2012/0038064A1

審查人員：古朝璟

## 【57】申請專利範圍

1. 一種製造一半導體裝置之方法，其係包括：提供一第一半導體晶粒；形成一導電層於該第一半導體晶粒的主動表面之上並且從該第一半導體晶粒的一中央區域延伸至該第一半導體晶粒的一週邊區域；在該第一半導體晶粒的該週邊區域中的該導電層之上形成複數個第一互連結構；提供一第二半導體晶粒，其包含形成於該第二半導體晶粒的主動表面之上的複數個凸塊，其中該第二半導體晶粒和凸塊的結合高度是小於該複數個第一互連結構的高度；將該第二半導體晶粒設置於一載體之上，而該複數個凸塊朝向該載體；將該第一半導體晶粒設置於該載體和該第二半導體晶粒之上，而該第一半導體晶粒的該主動表面朝向該載體和該第二半導體晶粒，留下在該第二半導體晶粒的背表面和該第一半導體晶粒的主動表面之間的一間隙，其中該第二半導體晶粒被設置在該複數個第一互連結構之間；將一囊封體設置於該載體之上以覆蓋該第一半導體晶粒以及第二半導體晶粒，包含在該複數個第一互連結構和該第二半導體晶粒之間並且在該第二半導體晶粒的整個該背表面之上的該間隙中；在沉積該囊封體之後移除該載體；以及在該第一半導體晶粒、該第二半導體晶粒和該囊封體之上形成一第二互連結構，其中該第二互連結構接觸該複數個第一互連結構和凸塊。

2. 如申請專利範圍第 1 項之方法，其中該複數個第一互連結構和凸塊接觸該載體留下在該第二半導體晶粒和該第一半導體晶粒之間的該間隙。

3. 如申請專利範圍第 1 項之方法，其中在移除該載體之後，該複數個凸塊從該囊封體向外延伸以接觸該第二互連結構。

4. 如申請專利範圍第 1 項之方法，其進一步包含：提供一包含該第一半導體晶粒的半導體晶圓；以及移除該半導體晶圓的一部分至一 30 至 100 微米的厚度。

5. 如申請專利範圍第 4 項之方法，其進一步包含在移除該半導體晶圓的該部分之前形成該複數個第一互連結構。

6. 一種製造一半導體裝置之方法，其係包括：提供一第一半導體晶粒；形成一第一互連結構以及一第二互連結構圍繞該第一半導體晶粒的一週邊；提供一第二半導體晶粒，其包含形成於該第二半導體晶粒的主動表面之上的複數個凸塊；將該第二半導體晶粒設置在一載體之上，而該複數個凸塊朝向該載體；將該第一半導體晶粒設置於在該複數個凸塊之上的該載體上，而該第二半導體晶粒在該第一互連結構以及該第二互連結構之間而留下在該第二半導體晶粒和該第一半導體晶粒之間的一間隙；將一囊封體設置在該載體、該第一半導體晶粒以及該第二半導體晶粒之上，其中該囊封體延伸在該間隙中於該第二半導體晶粒相對於該主動表面的整個一第二表面之上；以及在沉積該囊封體之後移除該載體。

7. 如申請專利範圍第 6 項之方法，其進一步包含在移除該載體之後，在該第一半導體晶粒、第二半導體晶粒和囊封體之上形成一第三互連結構。

8. 如申請專利範圍第 7 項之方法，其中該第一互連結構、該第二互連結構以及該複數個凸塊從該囊封體向外延伸以接觸該第三互連結構。

9. 如申請專利範圍第 6 項之方法，其進一步包含在該第一半導體晶粒的一中央區域以及該第一半導體晶粒的該週邊之間形成一導電層。

10. 如申請專利範圍第 6 項之方法，其進一步包含在該第一半導體晶粒的一中央區域之上設置該第二半導體晶粒。

11. 一種半導體裝置，其係包括：一第一半導體晶粒，其包含形成在該第一半導體晶粒的主動表面上圍繞該第一半導體晶粒的一週邊的一第一互連結構以及一第二互連結構；一第二半導體晶粒，其設置在該第一互連結構以及該第二互連結構之間的該第一半導體晶粒的該主動表面之上，其中該第二半導體晶粒包含形成於該第二半導體晶粒的主動表面之上遠離該第一半導體晶粒的複數個凸塊；以及一囊封體，其設置在該第一半導體晶粒以及該第二半導體晶粒之上且該囊封體的一表面在該第一半導體晶粒的該主動表面以及該第二半導體晶粒的該主動表面之上，其中該囊封體在該第一互連結構和該第二互連結構和第二半導體晶粒之間並且在該第一半導體晶粒和該第二半導體晶粒之間延伸，並且其中該第一半導體晶粒的該第一互連結構和第二半導體晶粒以及該第二半導體晶粒的該複數個凸塊從該囊封體的該表面曝露。

12. 如申請專利範圍第 11 項之半導體裝置，其中該第二半導體晶粒和凸塊的一高度總和是小於該第一互連結構的一高度。

13. 如申請專利範圍第 11 項之半導體裝置，其進一步包含形成在該第一半導體晶粒之上的一重新分佈層。

#### 圖式簡單說明

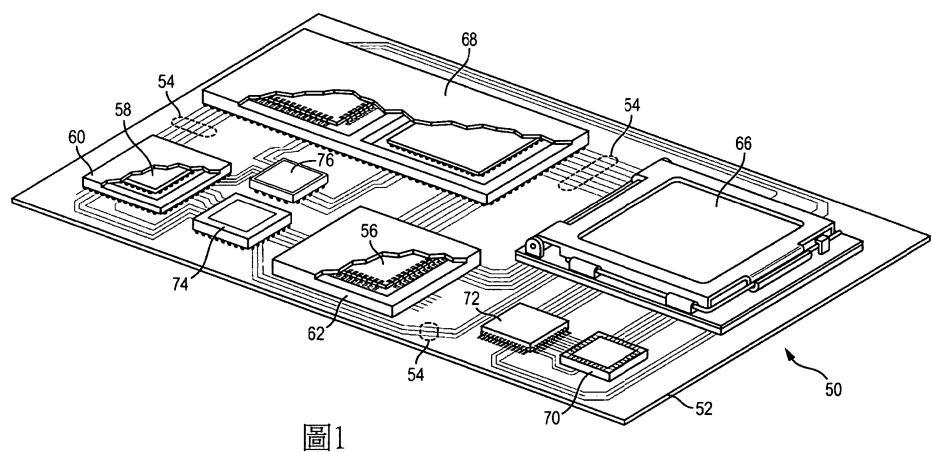

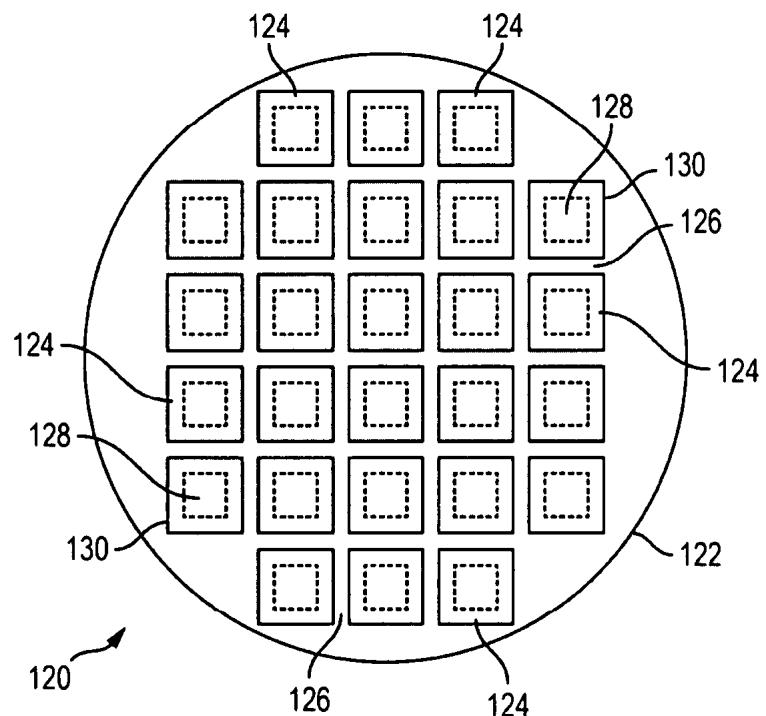

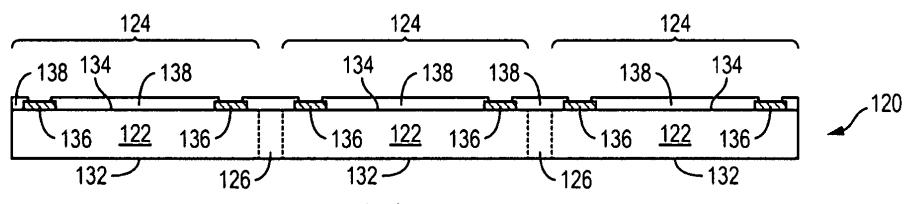

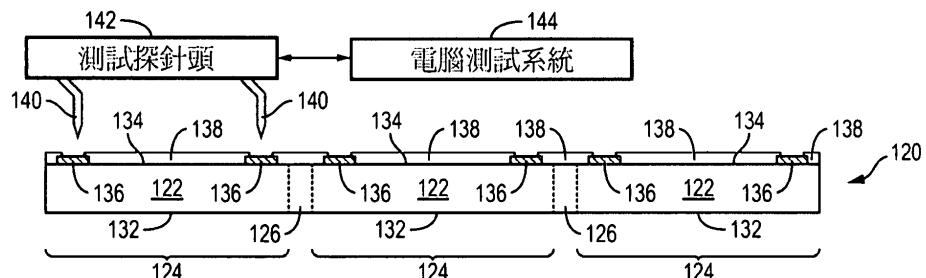

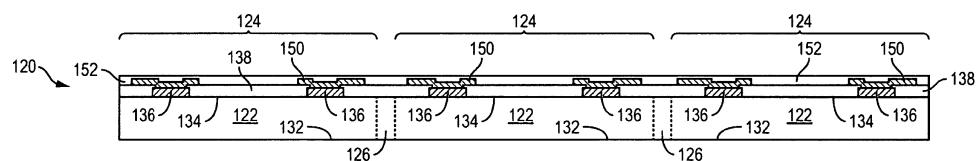

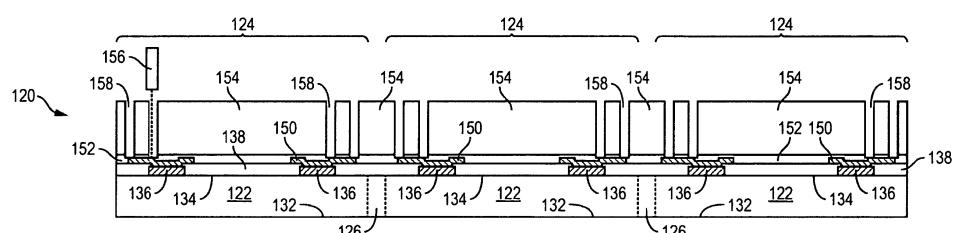

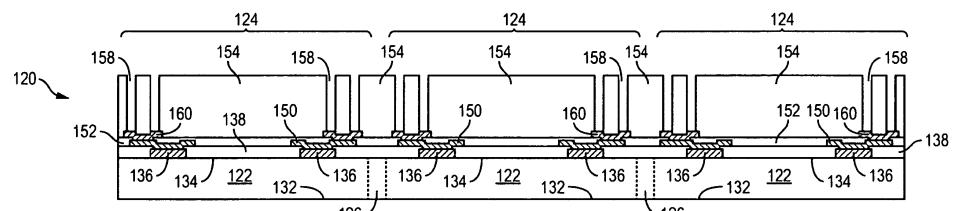

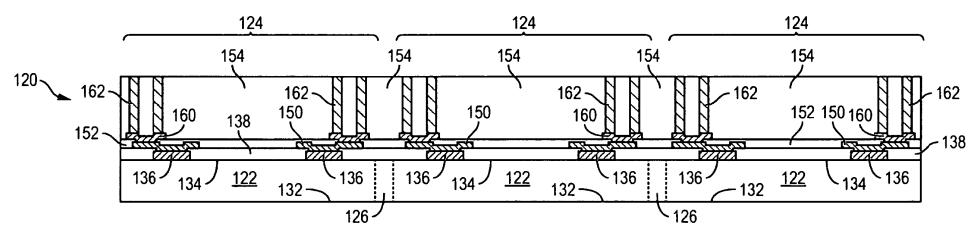

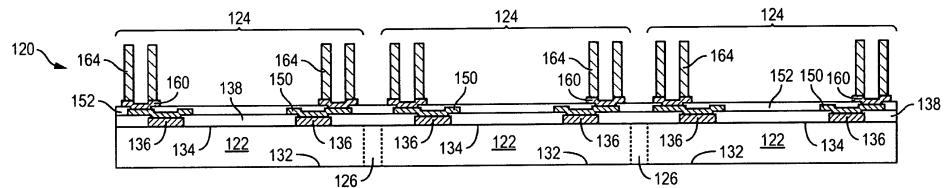

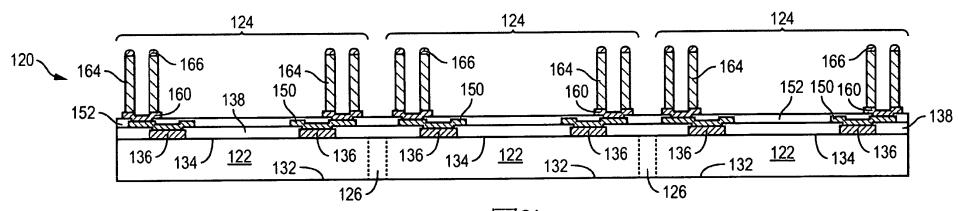

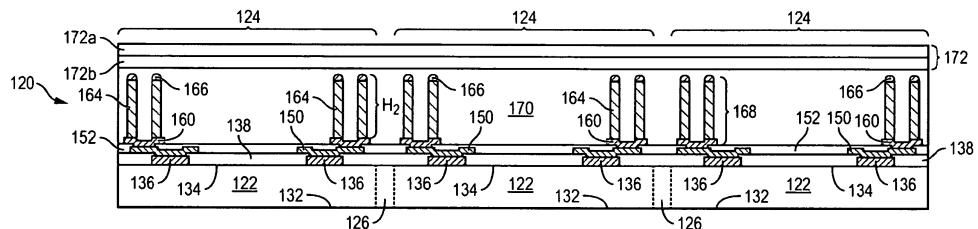

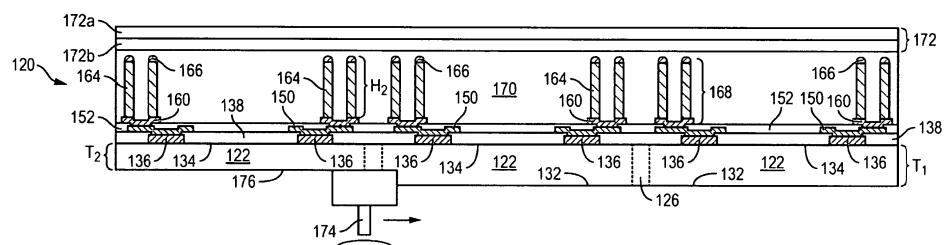

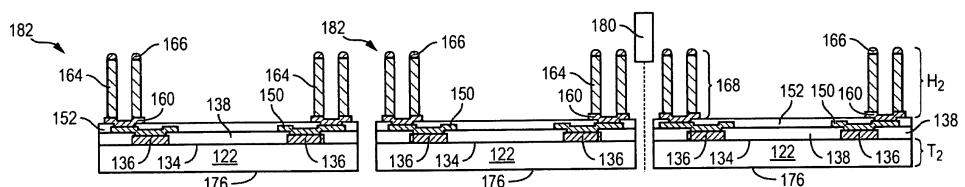

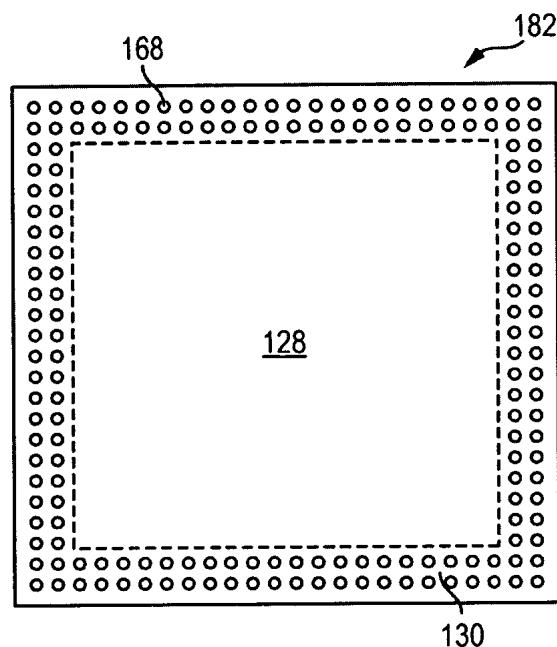

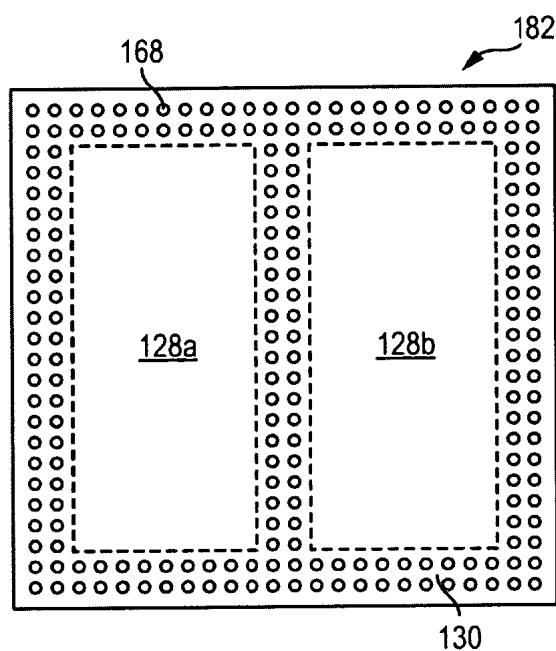

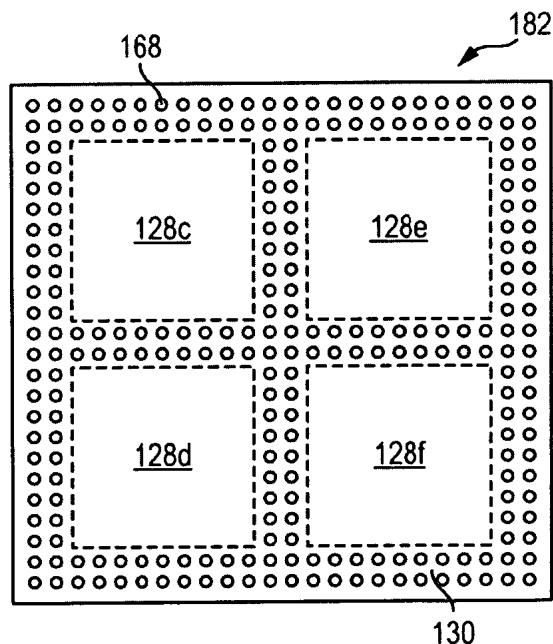

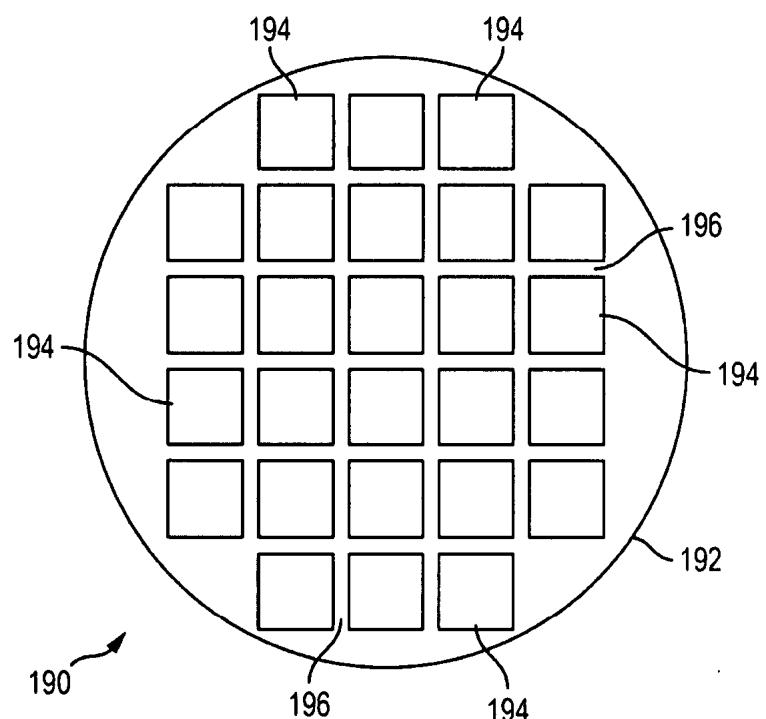

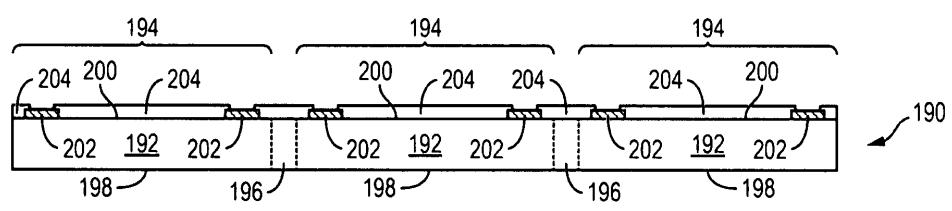

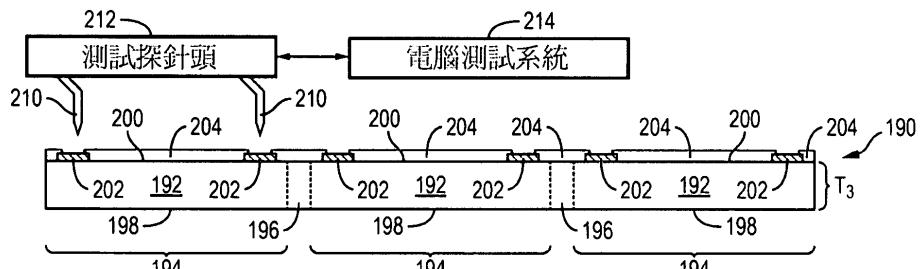

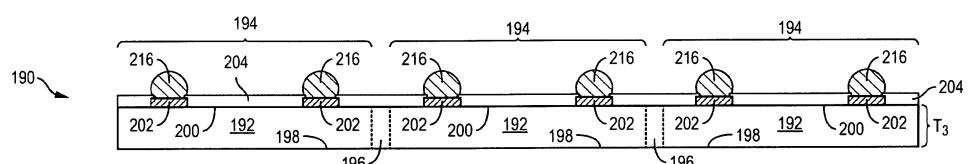

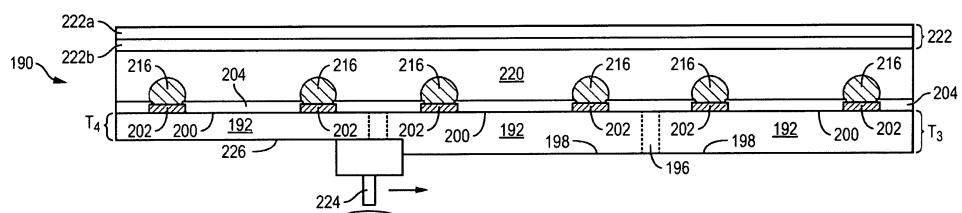

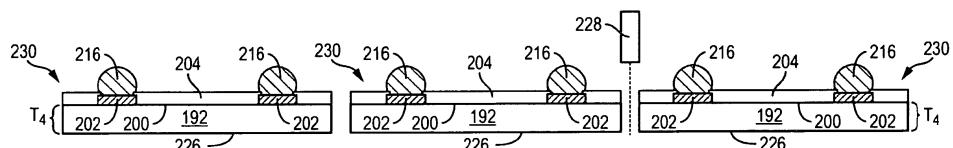

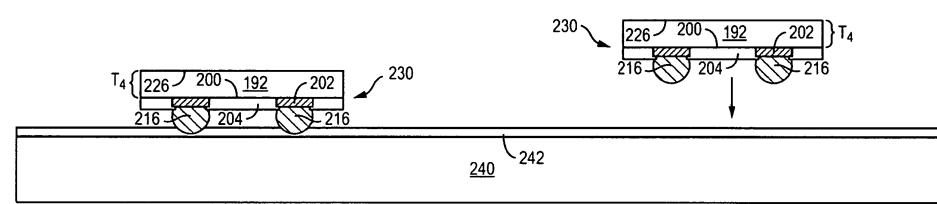

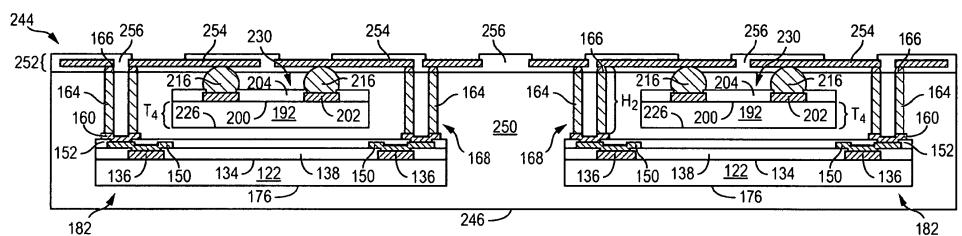

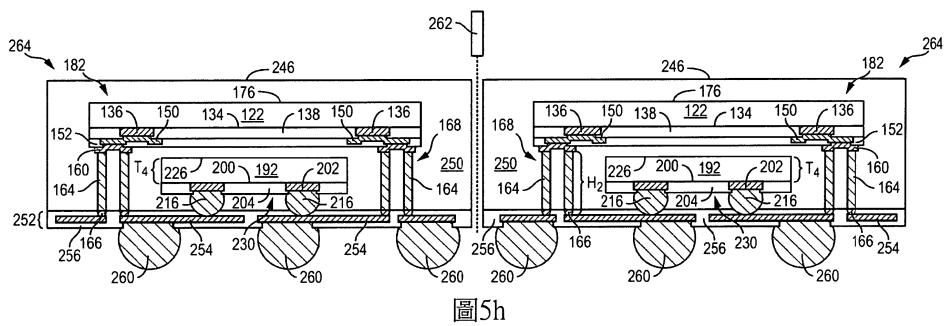

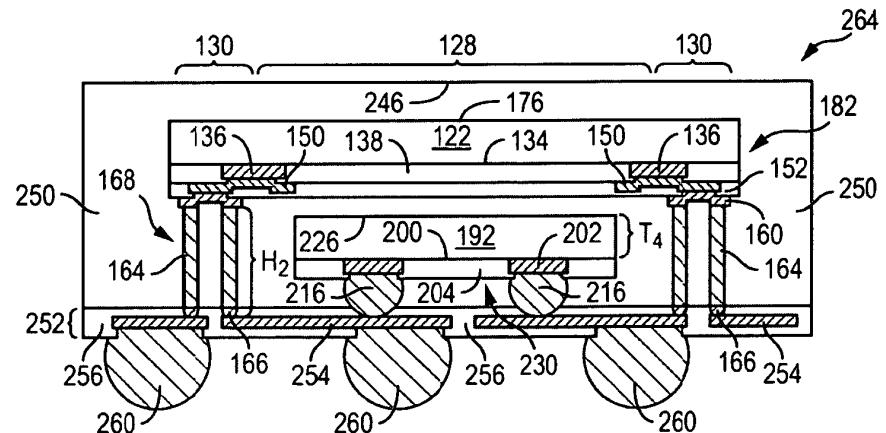

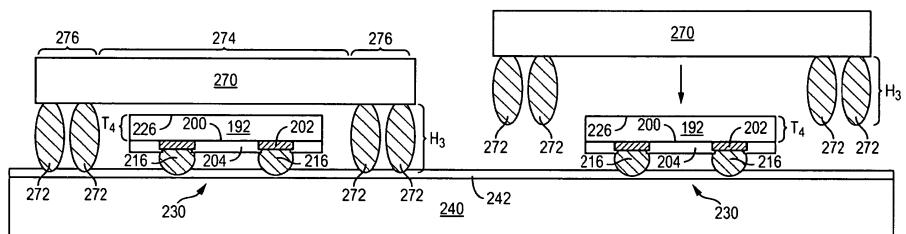

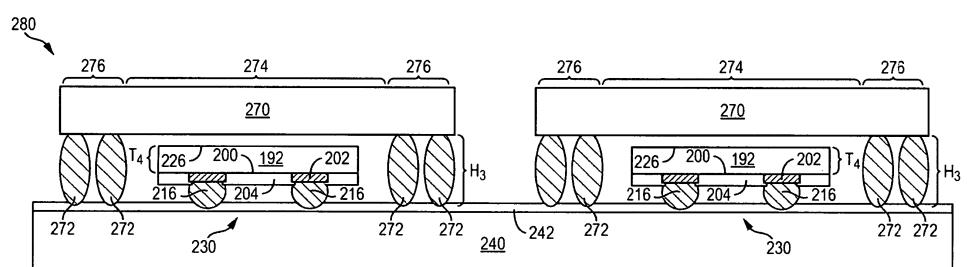

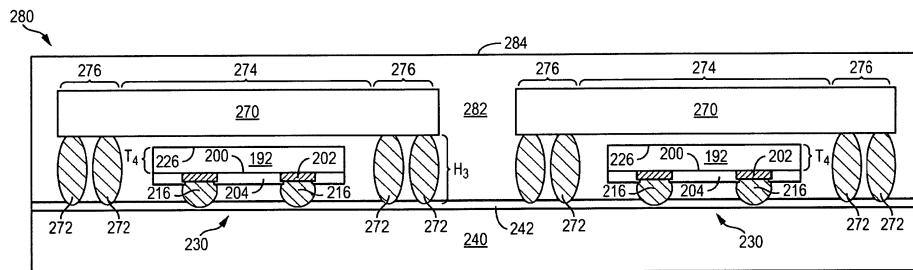

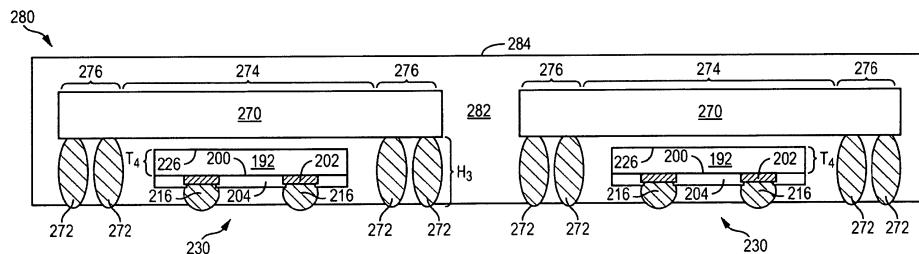

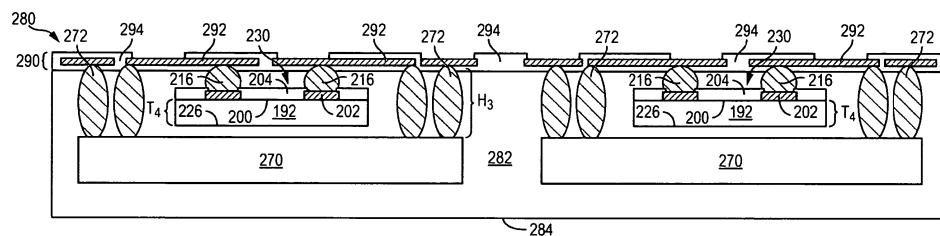

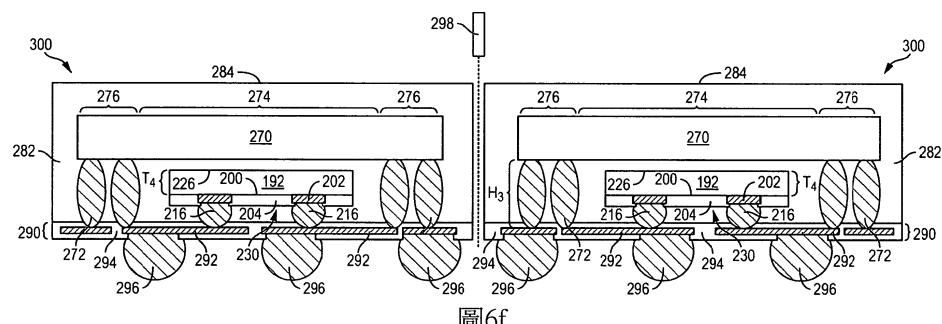

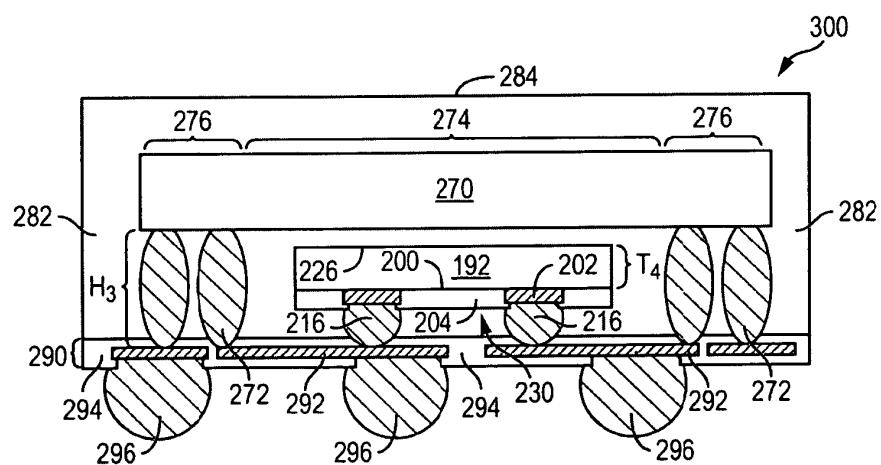

圖 1 係描繪一印刷電路板(PCB)，其中不同類型的封裝係安裝到該 PCB 的一表面；圖 2a-2l 係描繪一具有複數個藉由切割道分開的半導體晶粒之半導體晶圓；圖 3a-3c 係以平面圖來描繪圖 2a-2l 的半導體晶粒；圖 4a-4f 係描繪一具有複數個藉由切割道分開的半導體晶粒之半導體晶圓；圖 5a-5i 係描繪一利用單側 FO-WLCSP 來堆疊圖 2a-2l 及 4a-4f 的半導體晶粒的製程；以及圖 6a-6g 係描繪一利用單側 FO-WLCSP 來堆疊一半導體封裝以及圖 4a-4f 的半導體晶粒的製程。

(3)

圖 1

圖2a

圖2b

(4)

圖2c

圖2d

圖2e

圖2f

圖2g

(5)

圖2h

圖2i

圖2j

圖2k

圖2l

(6)

圖3a

圖3b

(7)

圖3c

圖4a

圖4b

圖4c

圖4d

圖4e

圖 4f

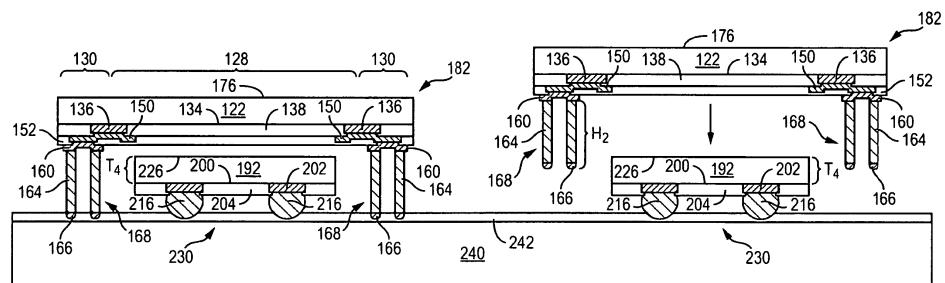

圖 5a

圖5b

(9)

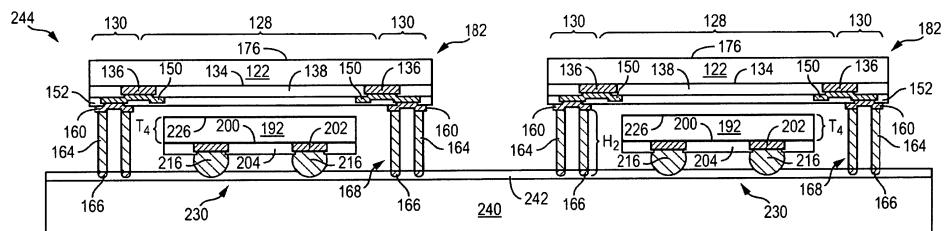

圖5c

圖5d

圖5e

圖5f

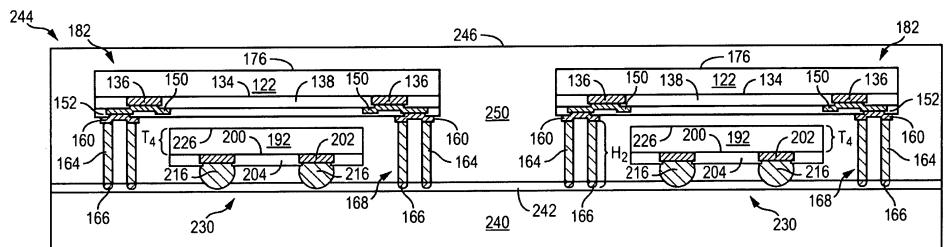

圖5g

(10)

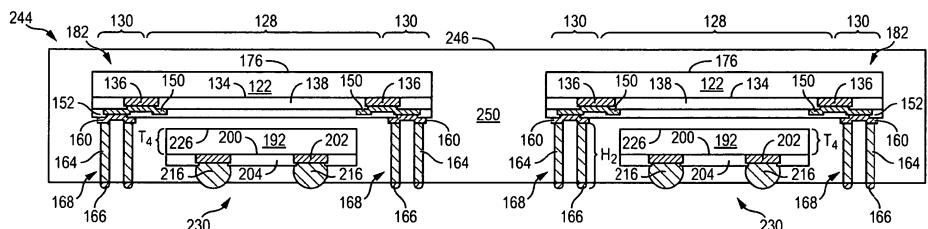

圖5h

圖5i

圖 6a

圖6b

(11)

圖6c

圖6d

圖6e

圖6f

圖6g