【11】證書號數：I661525

【45】公告日：中華民國 108(2019)年 06 月 01 日

|                |                             |                             |

|----------------|-----------------------------|-----------------------------|

| 【51】Int. Cl. : | <i>H01L23/525 (2006.01)</i> | <i>H01L23/498 (2006.01)</i> |

|                | <i>H01L23/31 (2006.01)</i>  | <i>H01L23/48 (2006.01)</i>  |

發明

全 23 頁

## 【54】名稱：半導體封裝及其製造方法

SEMICONDUCTOR PACKAGE AND METHOD FOR MANUFACTURING

THE SAME

【21】申請案號：107110171

【22】申請日：中華民國 107(2018)年 03 月 26 日

【11】公開編號：201917858

【43】公開日期：中華民國 108(2019)年 05 月 01 日

【30】優先權：2017/10/26

南韓 10-2017-0139983

【72】發明人：崔益準 (KR) CHOI, IK JUN ; 李在彥 (KR) LEE, JAE EAN ; 鄭光玉 (KR)

JEONG, KWANG OK ; 高永寬 (KR) KO, YOUNG GWAN ; 卞貞洙 (KR)

BYUN, JUNG SOO

【71】申請人：南韓商三星電機股份有限公司 SAMSUNG ELECTRO-MECHANICS

CO., LTD.

南韓

【74】代理人：葉璟宗；鄭婷文；詹富閔

## 【56】參考文獻：

TW 201642406A

TW 201709777A

CN 102056407A

CN 102969252A

審查人員：邱元玠

## 【57】申請專利範圍

1. 一種半導體封裝，包括：支撐構件，具有空穴並包括將彼此相對的第一表面及第二表面連接的配線結構；連接構件，在所述支撐構件的所述第二表面上並包括連接至所述配線結構的第一重佈線層；半導體晶片，在所述空穴中、在所述連接構件上並具有連接至所述第一重佈線層的連接墊；包封體，包封在所述空穴中的所述半導體晶片並覆蓋所述支撐構件的所述第一表面；以及第二重佈線層，包括配線圖案並具有連接通孔，所述配線圖案嵌入於所述包封體中且具有暴露的表面，所述連接通孔貫穿所述包封體以將所述配線結構及所述配線圖案彼此連接，其中所述連接通孔貫穿所述配線圖案。

2. 如申請專利範圍第 1 項所述的半導體封裝，其中所述配線圖案具有開放區域，且所述連接通孔位於所述配線圖案的所述開放區域中。

3. 如申請專利範圍第 1 項所述的半導體封裝，其中所述連接通孔具有中心部分凹陷的上表面。

4. 如申請專利範圍第 2 項所述的半導體封裝，其中所述連接通孔的與所述配線圖案接觸的第一區域的寬度大於所述連接通孔的與所述配線結構接觸的第二區域的寬度。

5. 如申請專利範圍第 1 項所述的半導體封裝，其中所述第二重佈線層的暴露的表面包括與所述包封體的表面實質上共面的上表面。

6. 一種半導體封裝，包括：支撐構件，具有空穴並包括將彼此相對的第一表面及第二表面連接的配線結構；連接構件，在所述支撐構件的所述第二表面上並包括連接至所述配線結構的第一重佈線層；半導體晶片，在所述空穴中、在所述連接構件上並具有連接至所述第一重佈線層的連接墊；包封體，包封在所述空穴中的所述半導體晶片並覆蓋所述支

撐構件的所述第一表面；絕緣層，具有彼此相對的第一表面及第二表面，所述第二表面與所述包封體接觸；以及第二重佈線層，包括嵌入於所述絕緣層的所述第一表面中的第一配線圖案以及在所述絕緣層的所述第二表面上並嵌入於所述包封體中的第二配線圖案，其中所述第二重佈線層包括第一連接通孔，所述第一連接通孔貫穿所述絕緣層及所述包封體、連接至所述第一配線圖案及所述第二配線圖案以及連接至所述配線結構。

7. 一種半導體封裝，包括：支撐構件，具有空穴並包括將彼此相對的第一表面及第二表面連接的配線結構；連接構件，在所述支撐構件的所述第二表面上並包括連接至所述配線結構的第一重佈線層；半導體晶片，在所述空穴中、在所述連接構件上並具有連接至所述第一重佈線層的連接墊；包封體，包封在所述空穴中的所述半導體晶片並覆蓋所述支撐構件的所述第一表面；絕緣層，具有彼此相對的第一表面及第二表面，所述第二表面與所述包封體接觸；以及第二重佈線層，包括嵌入於所述絕緣層的所述第一表面中的第一配線圖案以及在所述絕緣層的所述第二表面上並嵌入於所述包封體中的第二配線圖案，其中所述第二重佈線層包括第二連接通孔，所述第二連接通孔貫穿所述絕緣層及所述包封體、連接至所述第二配線圖案以及連接至所述配線結構，且其中所述第二連接通孔不與所述第一配線圖案直接接觸。

8. 如申請專利範圍第 6 項或第 7 項所述的半導體封裝，其中所述第二重佈線層包括層間通孔，所述層間通孔貫穿所述絕緣層並將所述第一配線圖案及所述第二配線圖案彼此連接。

9. 如申請專利範圍第 8 項所述的半導體封裝，其中所述層間通孔的與所述第二配線圖案接觸的第一部分的寬度大於所述層間通孔的與所述第一配線圖案接觸的第二部分的寬度。

10. 如申請專利範圍第 9 項所述的半導體封裝，其中所述層間通孔具有與所述第二配線圖案整合的結構。

11. 如申請專利範圍第 1 項所述的半導體封裝，其中所述第二重佈線層具有多個第一接墊區域，且具有暴露所述多個第一接墊區域的開口的第一鈍化層位於所述包封體的表面上。

12. 一種半導體封裝，包括：支撐構件，具有空穴並包括將彼此相對的第一表面及第二表面連接的配線結構；連接構件，在所述支撐構件的所述第二表面上並包括連接至所述配線結構的第一重佈線層；半導體晶片，在所述空穴中、在所述連接構件上並具有連接至所述第一重佈線層的連接墊；包封體，包封在所述空穴中的所述半導體晶片並覆蓋所述支撐構件的所述第一表面；以及第二重佈線層，包括：絕緣層，具有彼此相對的第一表面及第二表面；第一配線圖案，嵌入於所述絕緣層的所述第一表面中；第二配線圖案，位於所述絕緣層的所述第二表面上並嵌入於所述包封體中；連接通孔，貫穿所述絕緣層及所述包封體以將所述第一配線圖案及所述第二配線圖案中的至少一者與所述配線結構彼此連接，所述第二表面與所述包封體接觸。

13. 一種半導體封裝，包括：支撐構件，包括將所述支撐構件的上表面連接至所述支撐構件的下表面的配線結構；連接構件，在所述支撐構件的所述下表面上並包括連接至所述配線結構的第一重佈線層；一或多個組件，在所述支撐構件的一或多個空穴中；包封體，覆蓋所述一或多個組件及所述支撐構件的所述上表面；第二重佈線層，位於所述支撐構件的所述上表面上方並包括嵌入於所述包封體中的配線圖案以及在所述第二重佈線層的上表面暴露的電極接墊；第一導電通孔，貫穿所述配線圖案的第一部分、在所述配線圖案的所述第一部分上方延伸、在所述配線圖案的所述第一部分下方延伸至所述包封體中並連接至所述支撐構件的所述上表面，其中所述第一重佈線層透過所述支撐構件的所述配線結構、所述第一導電通孔及所述第二重佈線層的所述配線圖案連接至所述第二重佈線層的所述電極接墊。

14. 如申請專利範圍第 13 項所述的半導體封裝，進一步包括：第二導電通孔，貫穿所述配線圖案的第二部分，在所述配線圖案的所述第二部分的下方延伸至所述包封體中並連接至

(3)

- 所述支撐構件的所述上表面，其中所述第二導電通孔的上表面與所述配線圖案的所述第二部分的上表面實質上共面。

15. 如申請專利範圍第 14 項所述的半導體封裝，其中所述第二連接通孔的所述上表面的中心部分是凹陷的。

16. 如申請專利範圍第 13 項所述的半導體封裝，進一步包括：層間通孔，位於所述第二重佈線層內並將嵌入於所述包封體中的所述配線圖案的下部連接至所述配線圖案的在所述下部上方的上部，其中所述層間通孔的與所述配線圖案的所述上部接觸的上寬度小於所述層間通孔的與所述配線圖案的所述下部接觸的下寬度，且其中在所述配線圖案的所述第一部分的上方的所述第一導電通孔的上寬度大於在所述配線圖案的所述第一部分的下方的所述第一導電通孔的下寬度。

17. 一種製造半導體封裝的方法，包括以下步驟：在支撐構件中形成空穴，所述支撐構件包括將所述支撐構件的下表面連接至所述支撐構件的上表面的配線結構；將半導體晶片配置在所述支撐構件的所述空穴中；在所述支撐構件上方、所述半導體晶片上方以及所述支撐構件的所述空穴中形成包封體；將上配線圖案嵌入於所述包封體中；在將所述上配線圖案嵌入之後，在所述包封體中形成將所述上配線圖案連接至所述支撐構件的所述上表面的一或多個孔洞；及在所述包封體中的所述一或多個孔洞中分別形成導電通孔。

18. 如申請專利範圍第 17 項所述的製造半導體封裝的方法，其中藉由在所述包封體硬化之前，在所述包封體的上表面層壓而將所述上配線圖案嵌入於所述包封體中。

19. 如申請專利範圍第 18 項所述的製造半導體封裝的方法，其中所述層壓包括：在臨時支撐體的離型層上形成配線圖案；將所述臨時支撐體層壓在所述包封體的上表面，其中所述配線圖案面向所述包封體並被轉移到包封體；及移除所述臨時支撐體。

20. 如申請專利範圍第 19 項所述的製造半導體封裝的方法，其中所述臨時支撐體的所述離型層上的所述配線圖案藉由以下步驟形成：在所述臨時支撐體的所述離型層上形成第一配線層；在所述第一配線層上形成絕緣層；以及在所述絕緣層上形成第二配線層，其中所述第一配線層及所述第二配線層藉由通孔穿過所述絕緣層而連接，及其中至少所述第二配線層嵌入於所述包封體中。

#### 圖式簡單說明

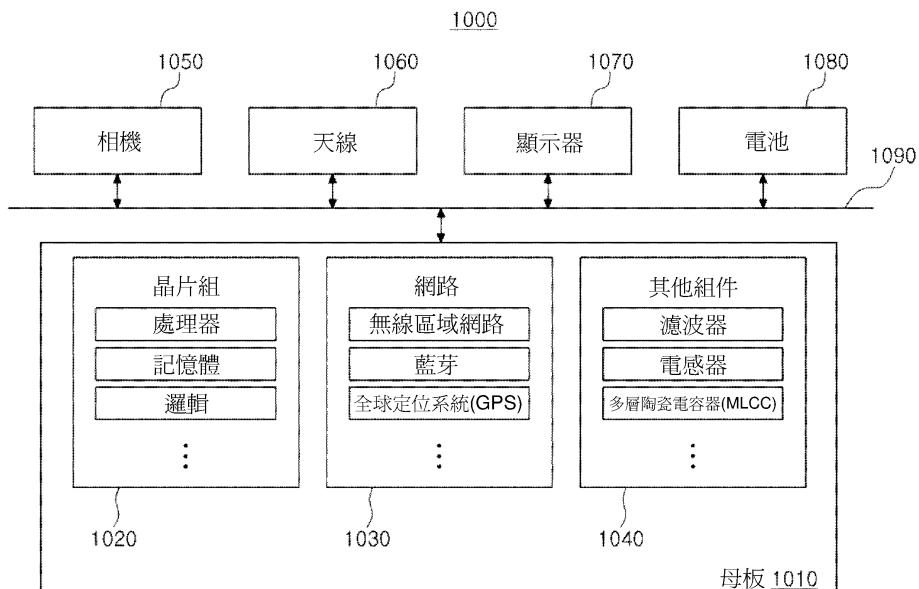

為讓本揭露的上述及其他樣態、特徵及優點更明顯易懂，下文特舉實施例，並配合所附圖式作詳細說明如下：圖 1 為說明電子裝置系統的一實施例的方塊示意圖。

圖 2 為說明電子裝置的一實例的立體示意圖。

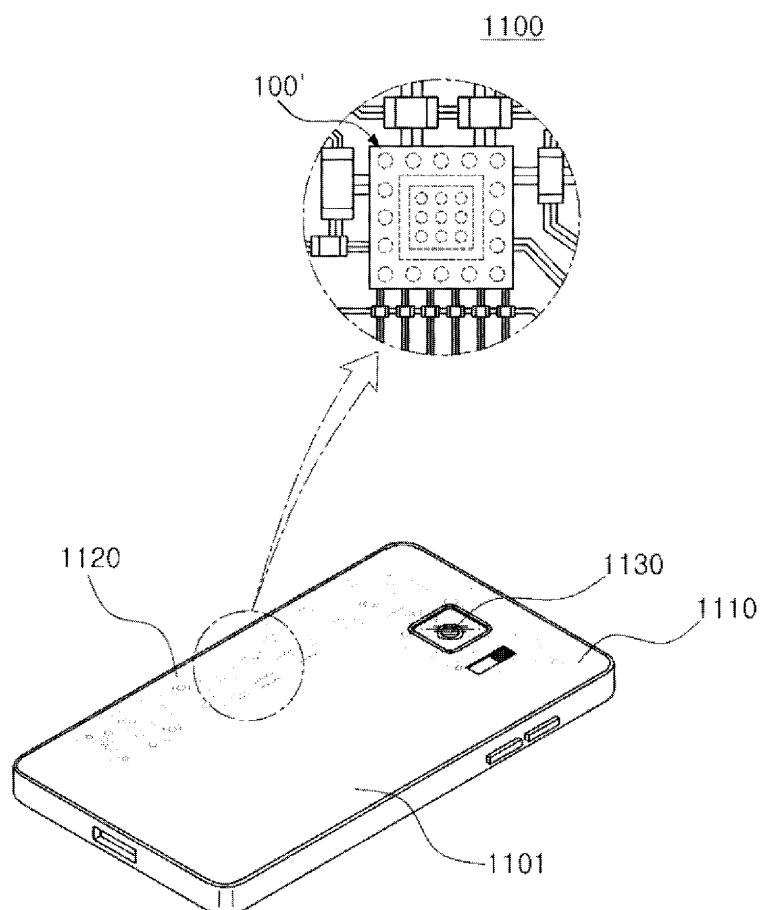

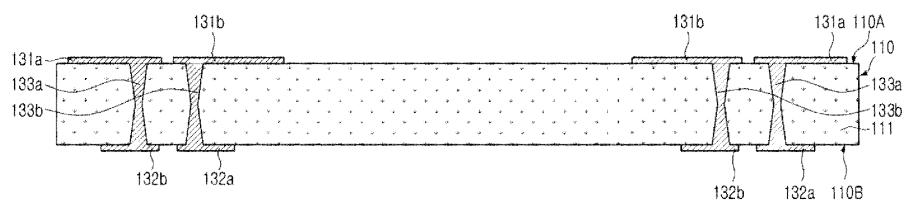

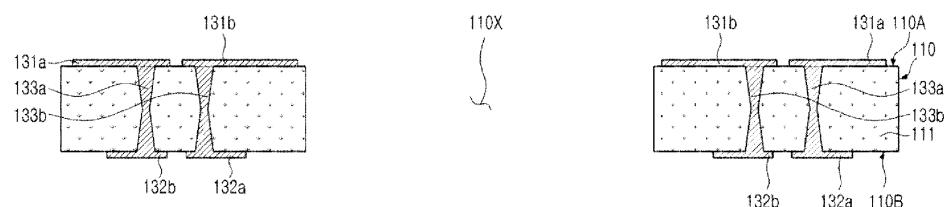

圖 3A 及圖 3B 為說明扇入型半導體封裝在封裝前及封裝後狀態的剖面示意圖。

圖 4 為說明扇入型半導體封裝的封裝製程的剖面示意圖。

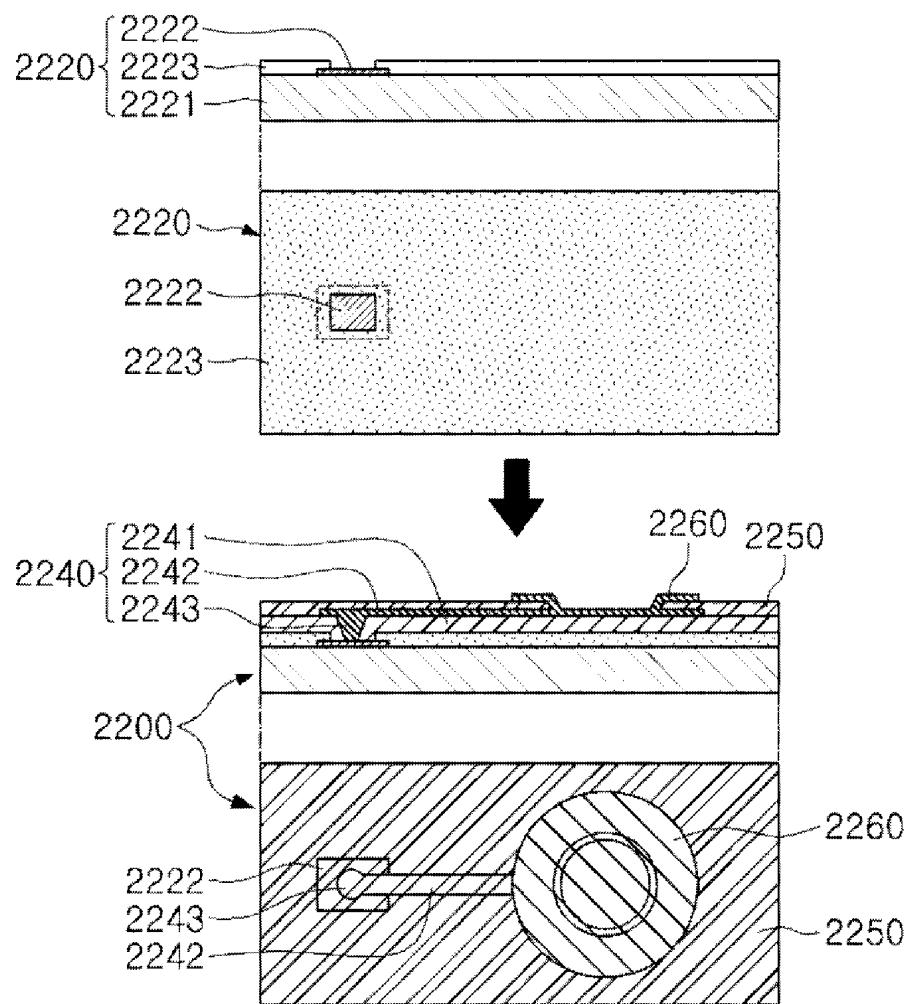

圖 5 為說明扇入型半導體封裝安裝於中介基板上且最終安裝於電子裝置主板上之情形的剖面示意圖。

圖 6 為說明扇入型半導體封裝嵌入中介基板中且最終安裝於電子裝置的主板上之情形的剖面示意圖。

圖 7 為說明扇出型半導體封裝的剖面示意圖。

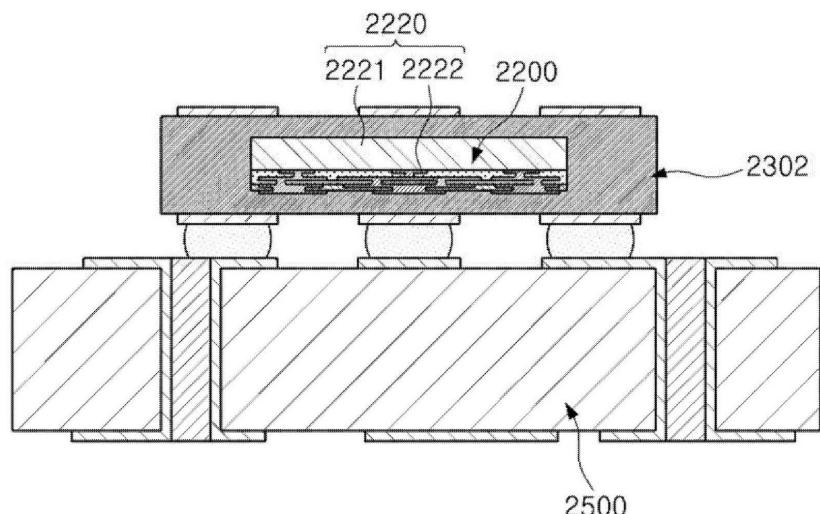

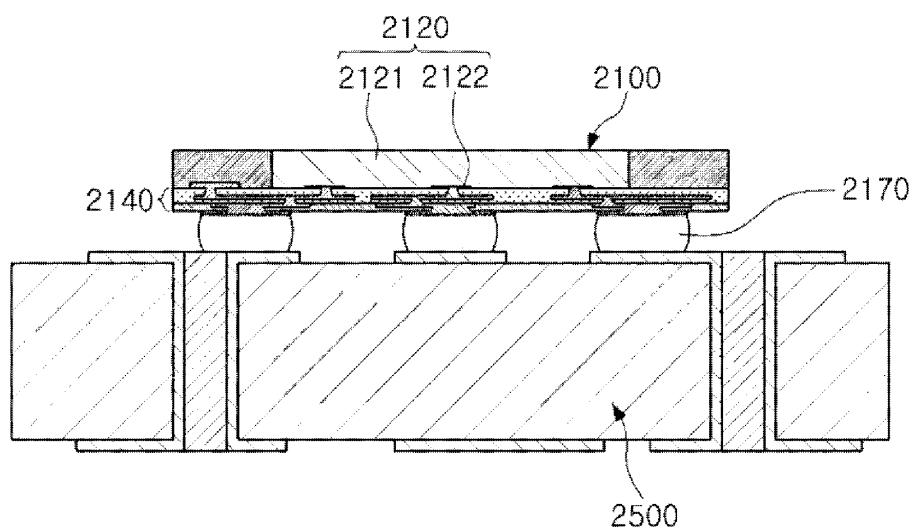

圖 8 為說明扇出型半導體封裝安裝於電子裝置的主板上之情形的剖面示意圖。

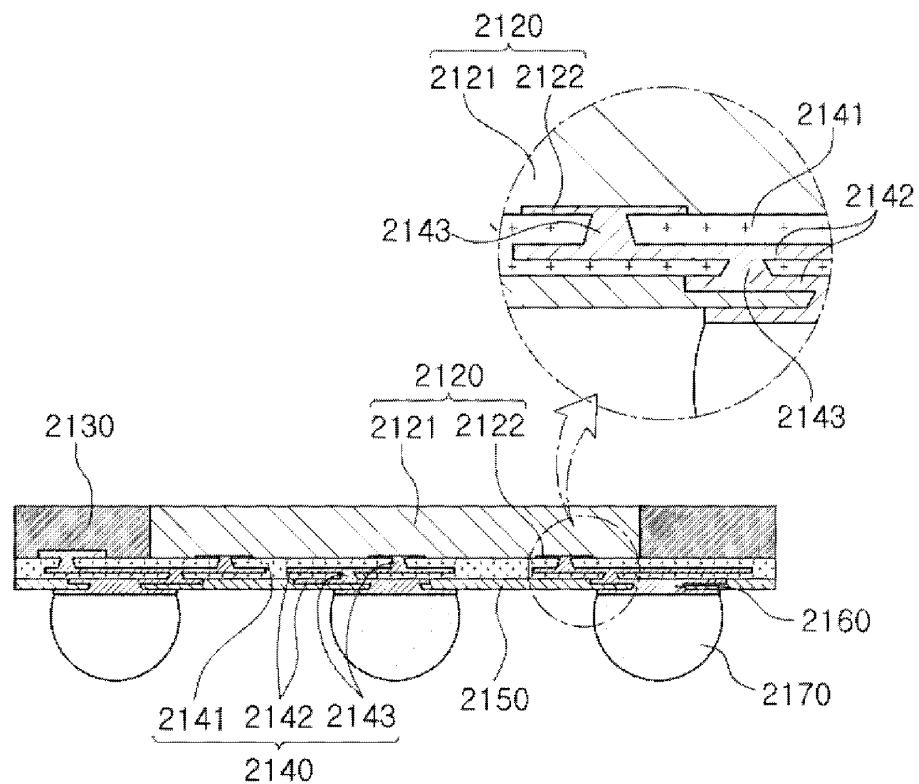

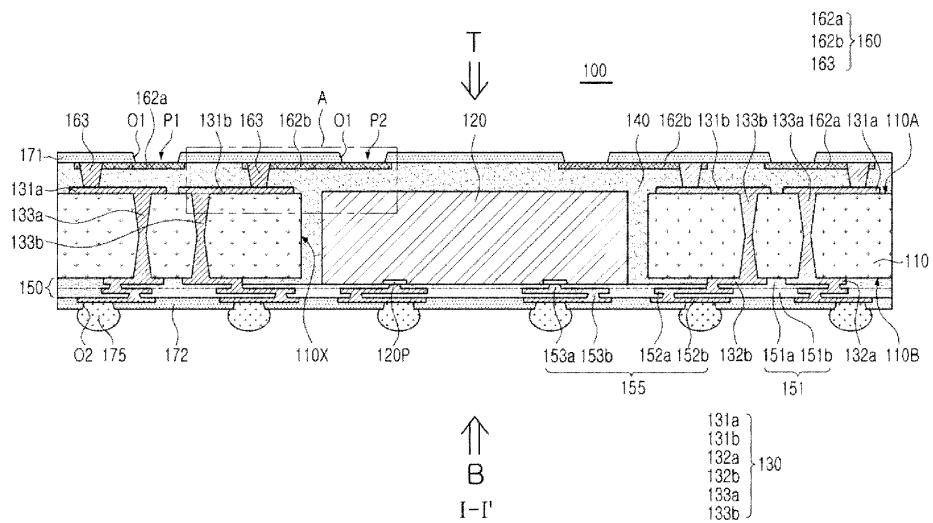

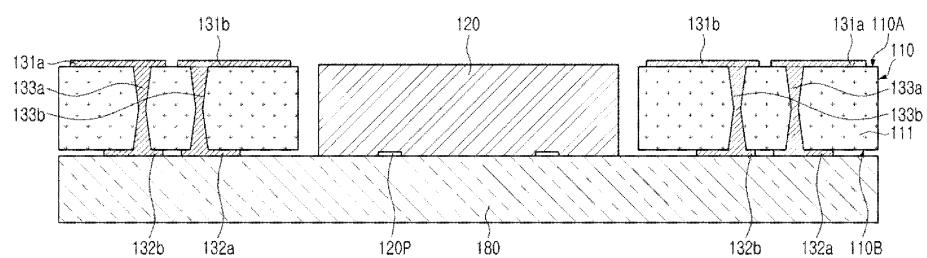

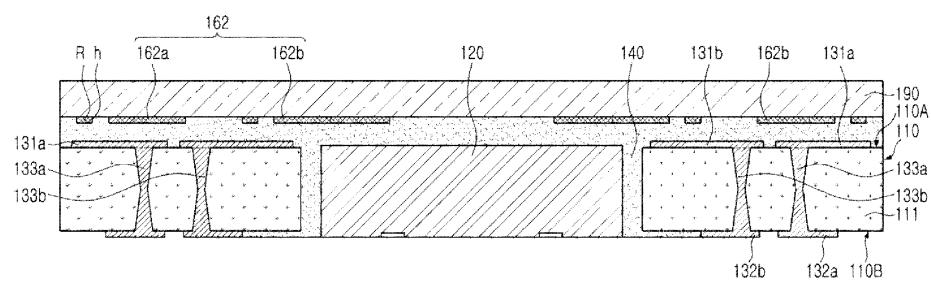

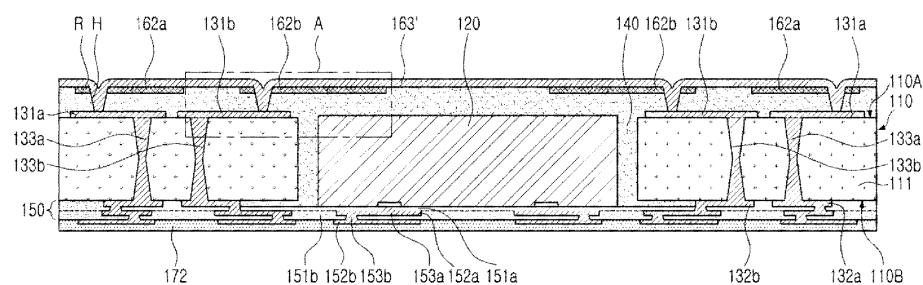

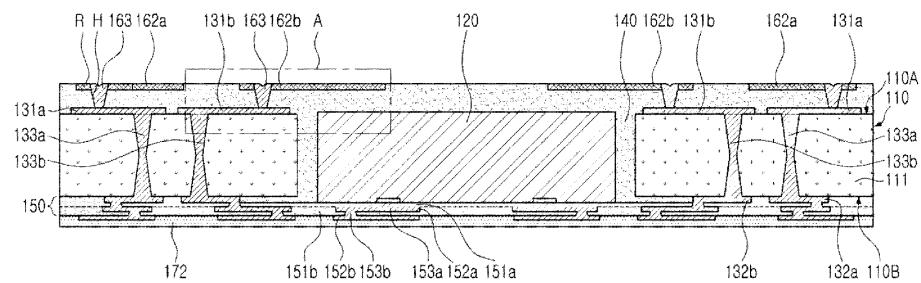

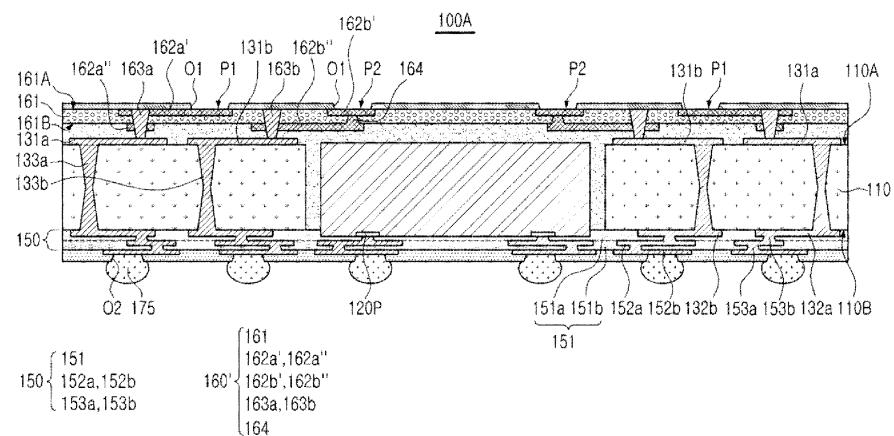

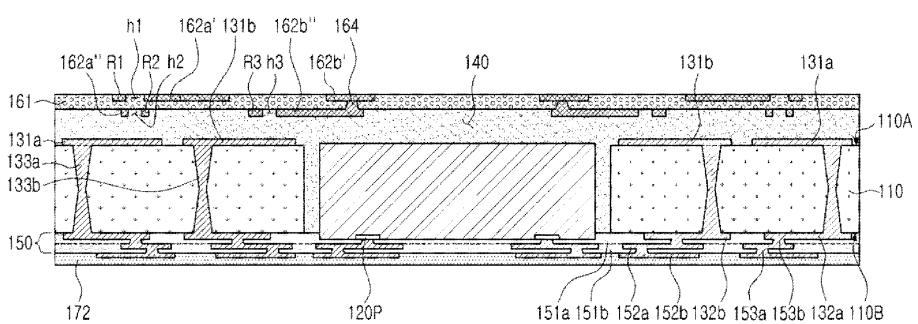

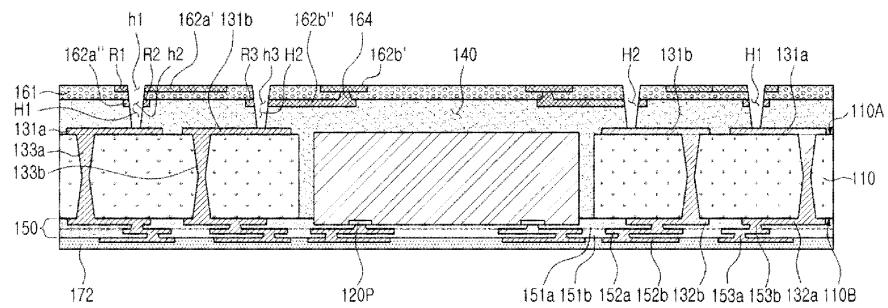

圖 9 為說明根據本揭露的一例示性實施例的扇出型半導體封裝的側視剖面圖。

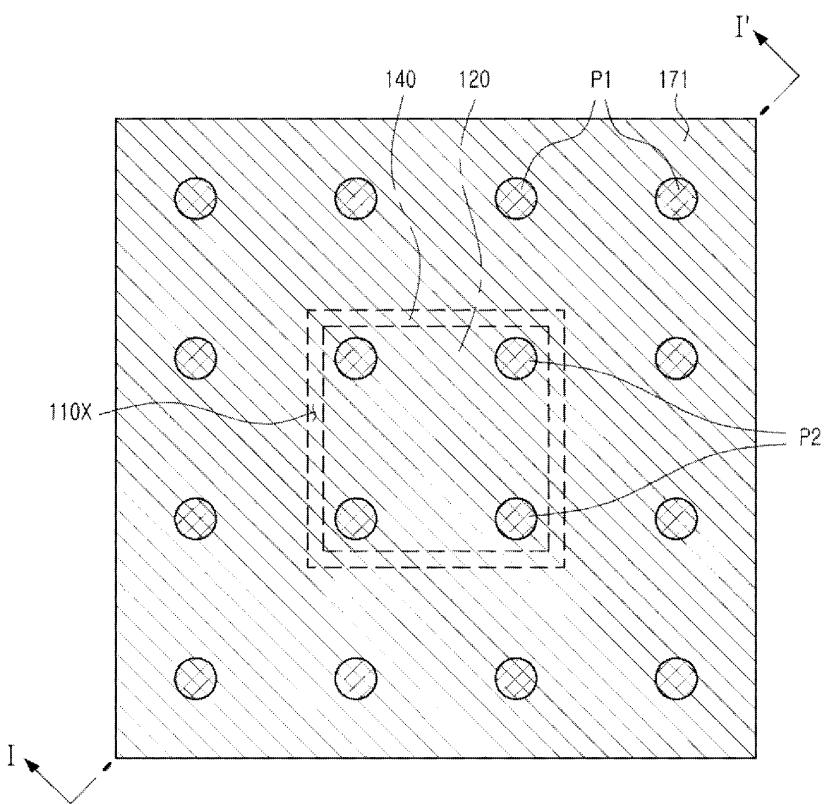

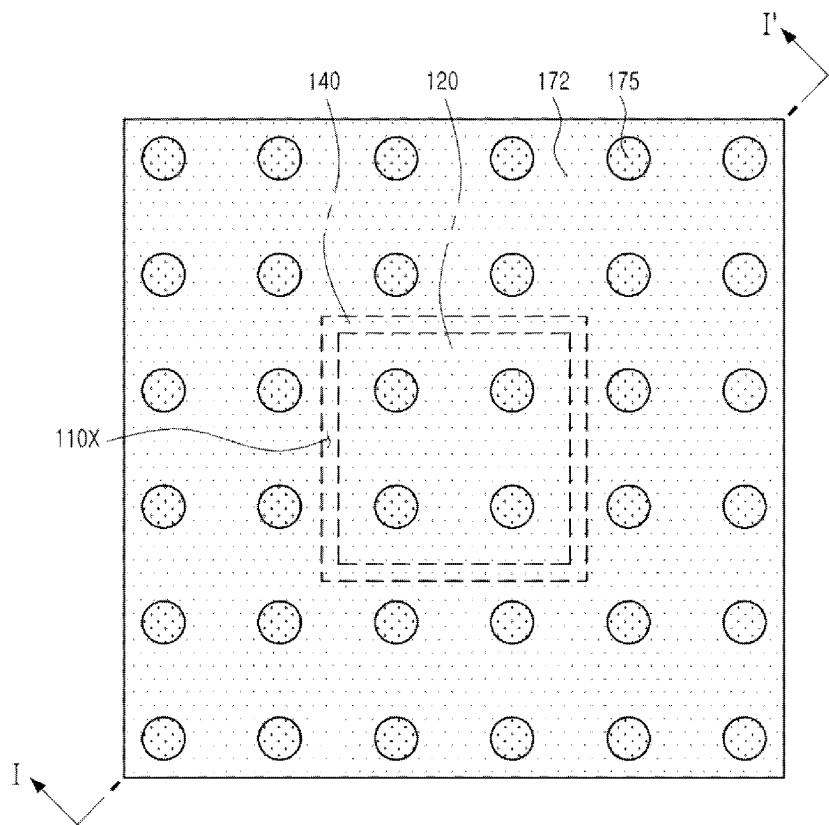

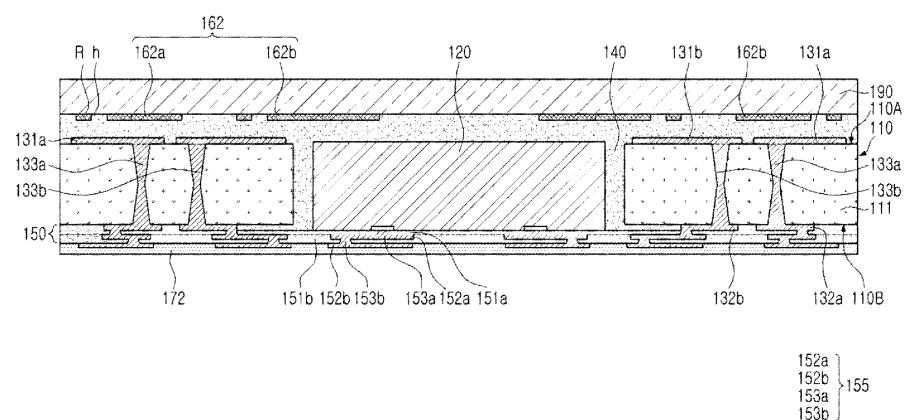

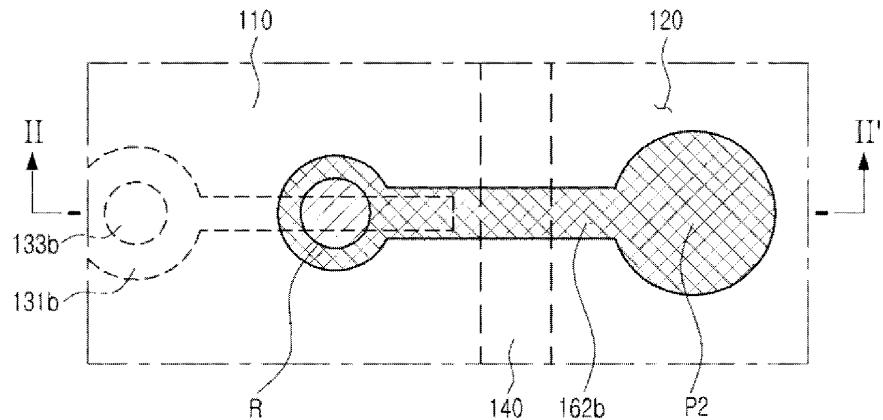

圖 10A 及圖 10B 分別為說明於圖 9 所繪示的扇出型半導體封裝的平面圖及底視圖。

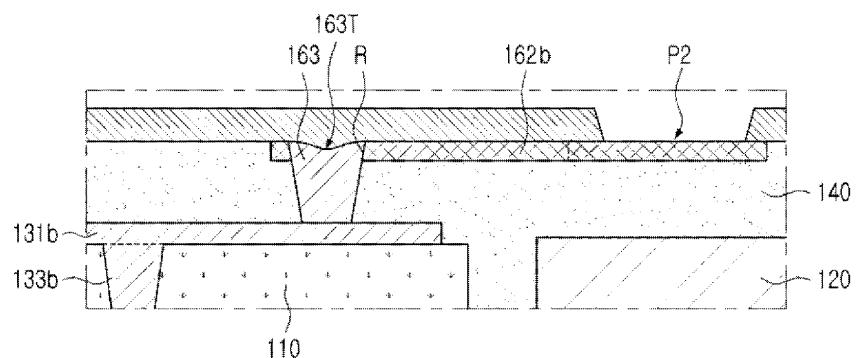

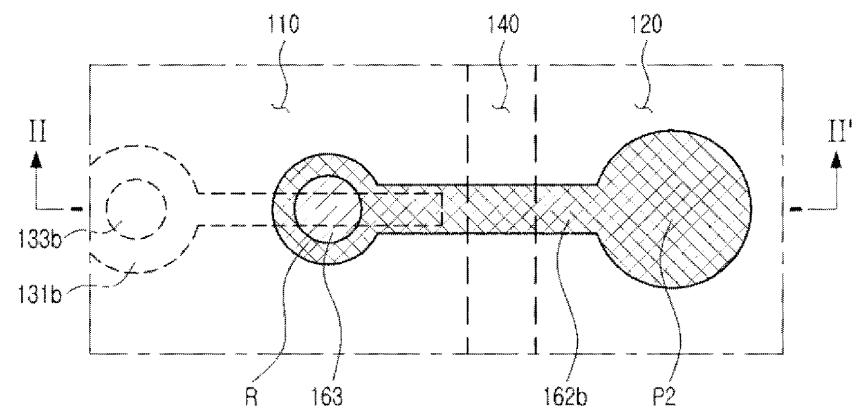

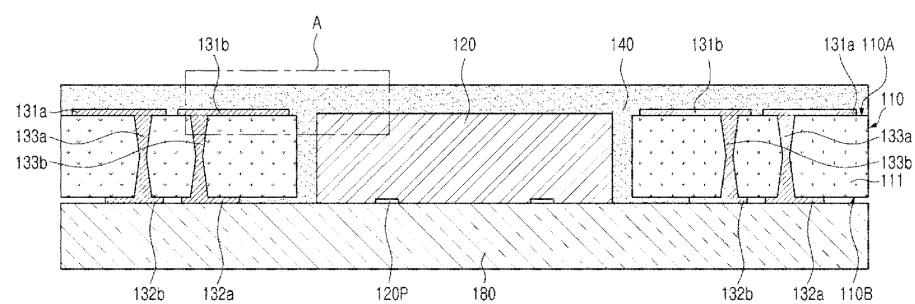

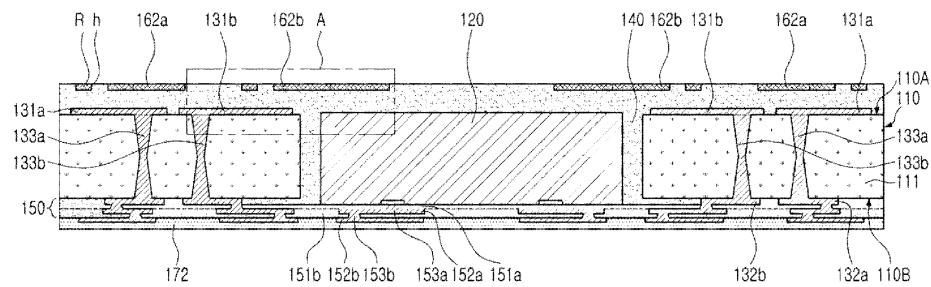

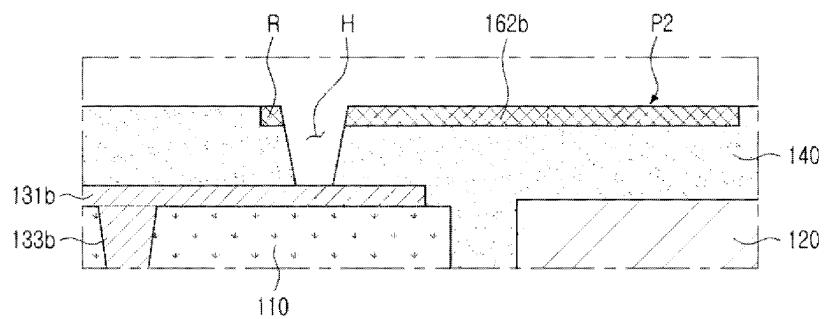

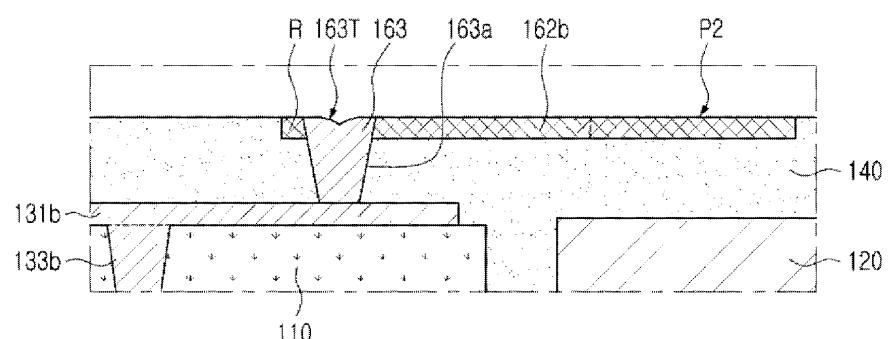

圖 11A 及圖 11B 分別為說明於圖 9 所繪示的扇出型半導體封裝的區域(A 部分)的放大剖面圖及平面圖。

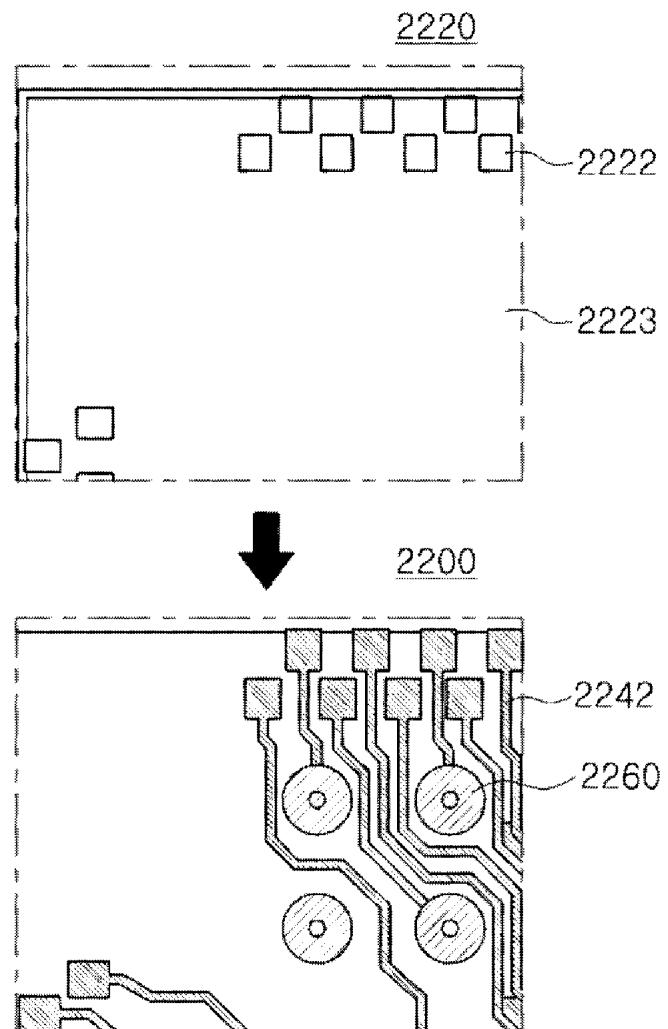

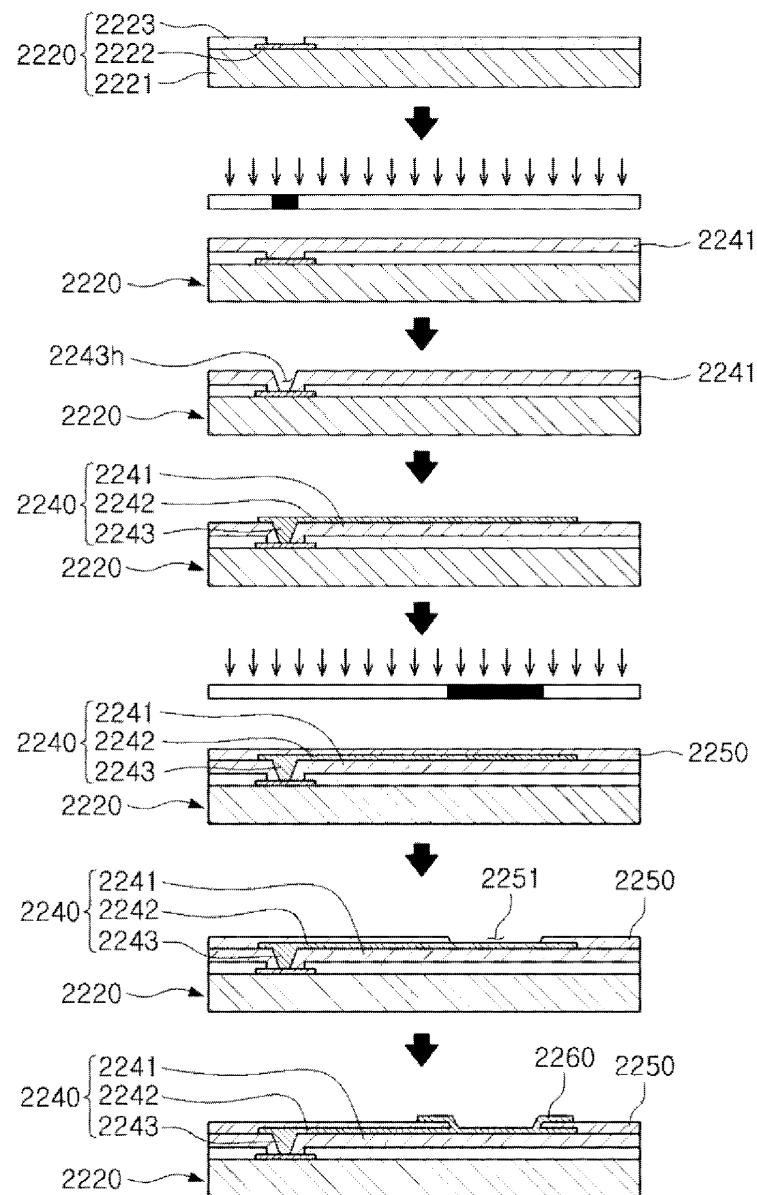

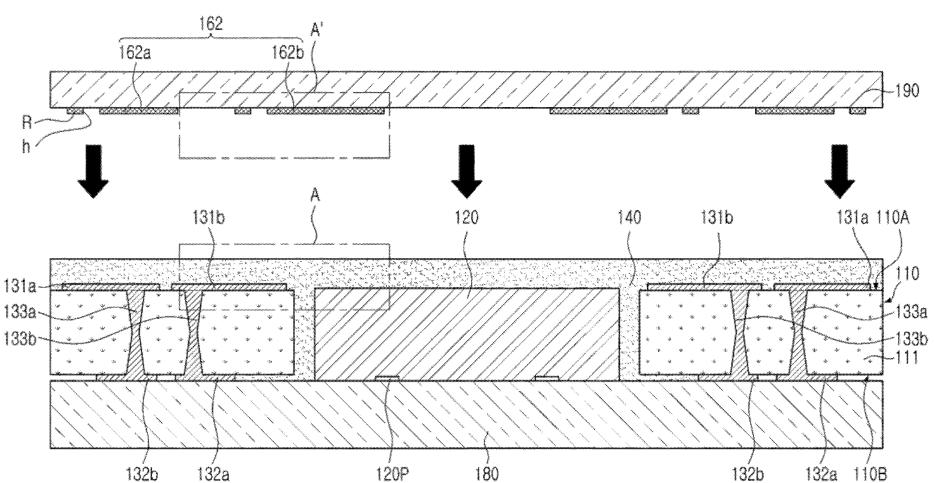

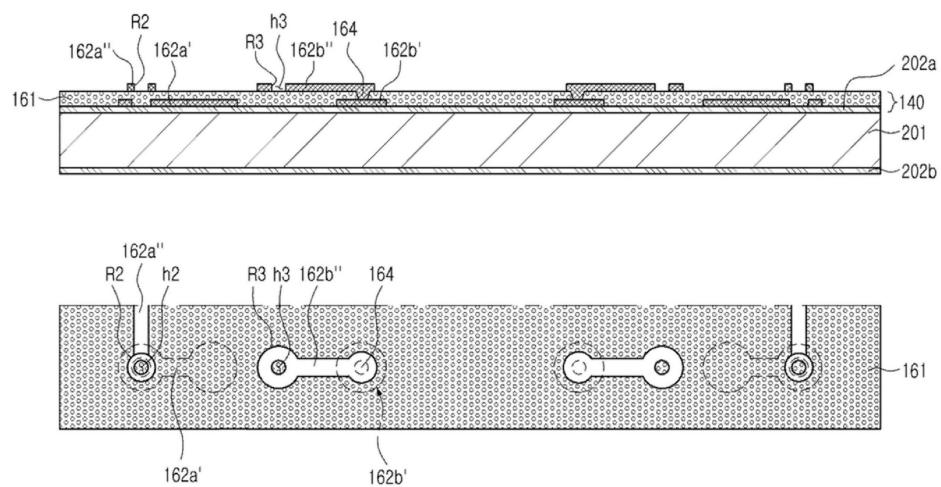

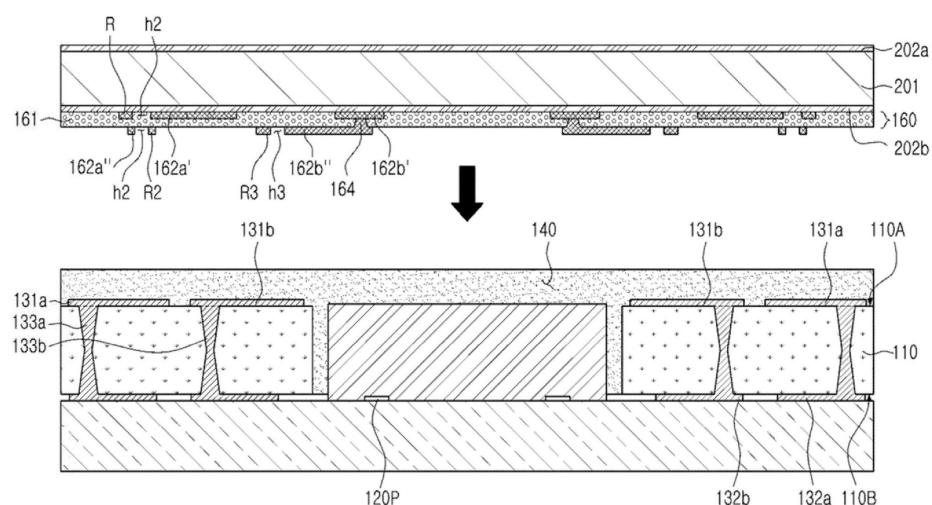

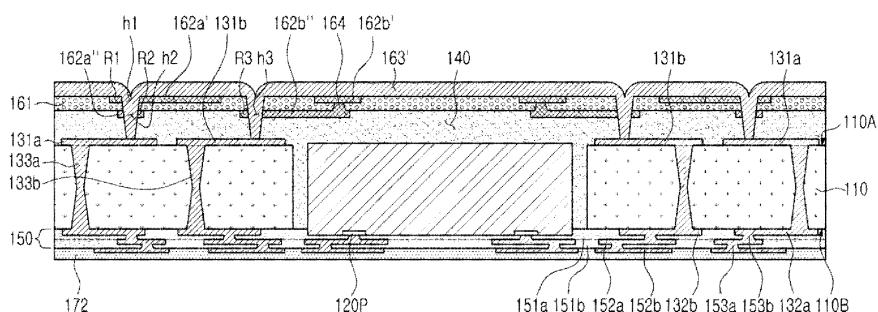

圖 12A 到圖 12H 為說明製造於圖 9 所繪示的扇出型半導體封裝的方法的形成第一重佈線層的製程及層壓製程的剖面圖。

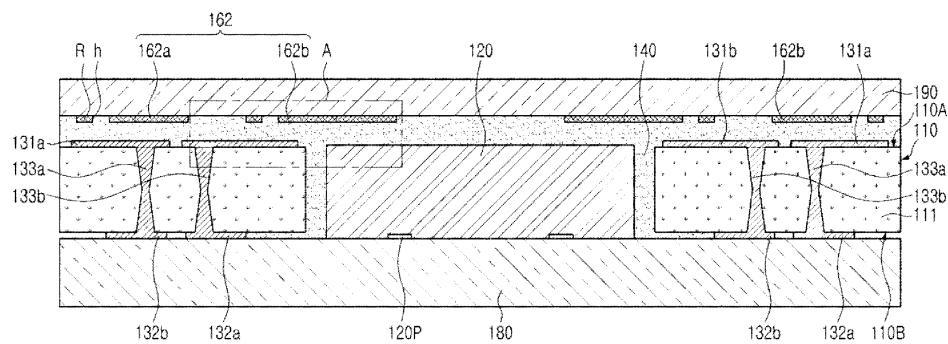

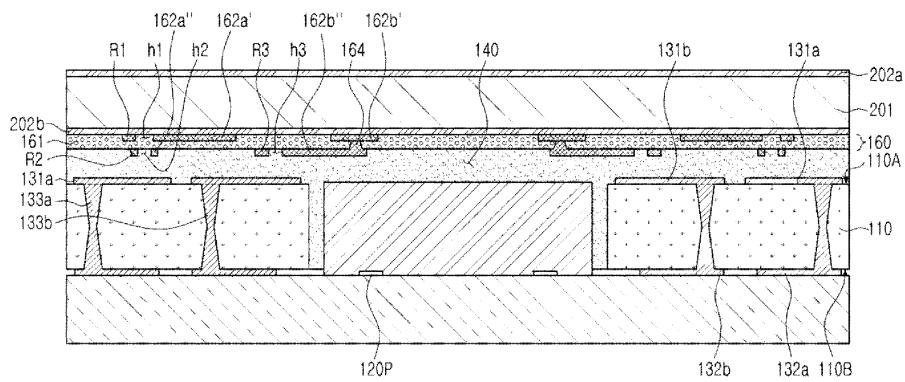

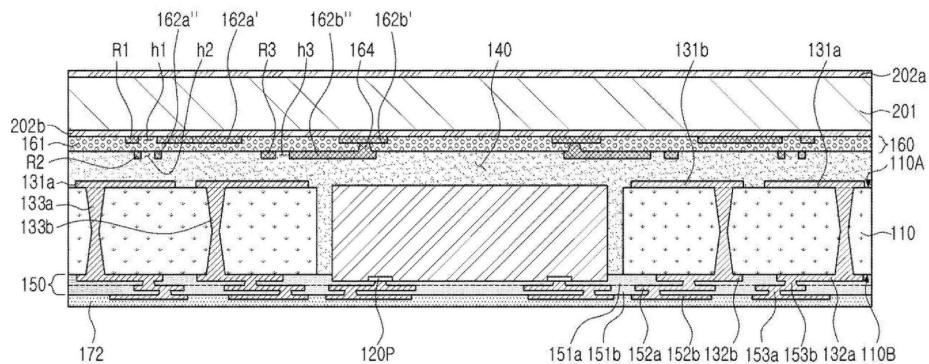

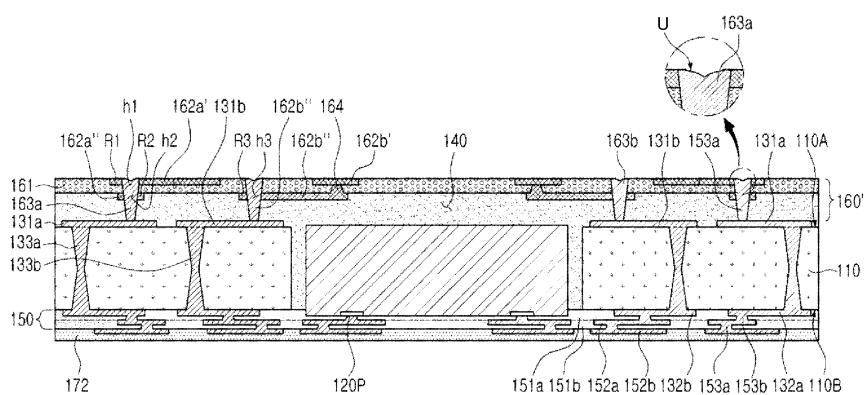

圖 13A 到圖 13D 為說明製造於圖 9 所繪示的扇出型半導體封裝的方法的形成連接通孔的製程的剖面圖。

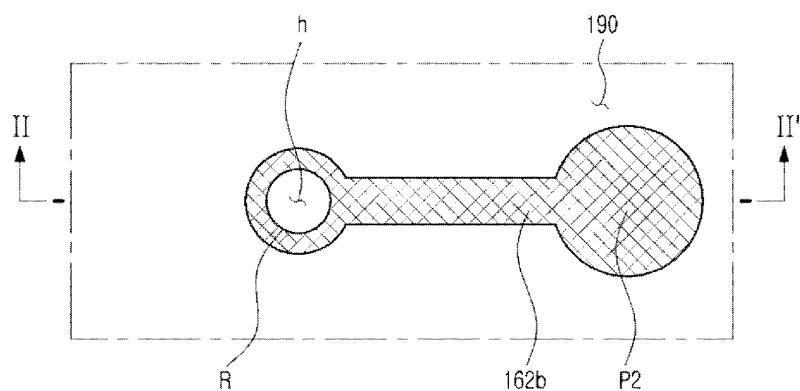

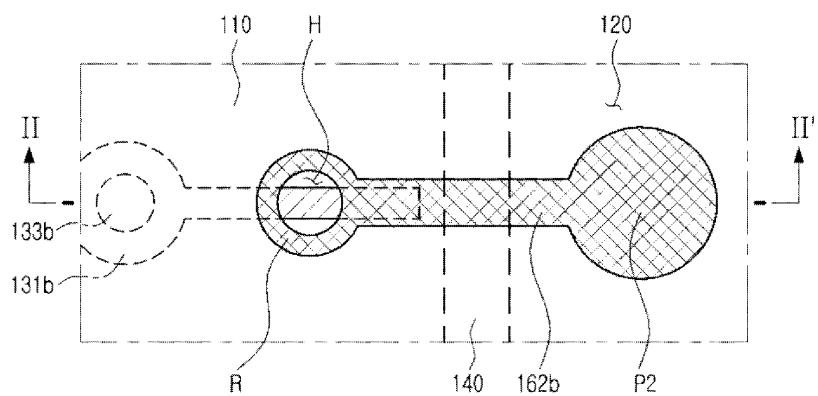

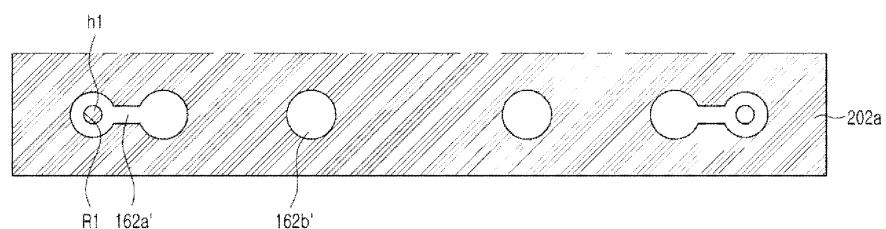

圖 14 為說明於圖 12E 所繪示的重佈線層的區域(部分 A')的平面圖。

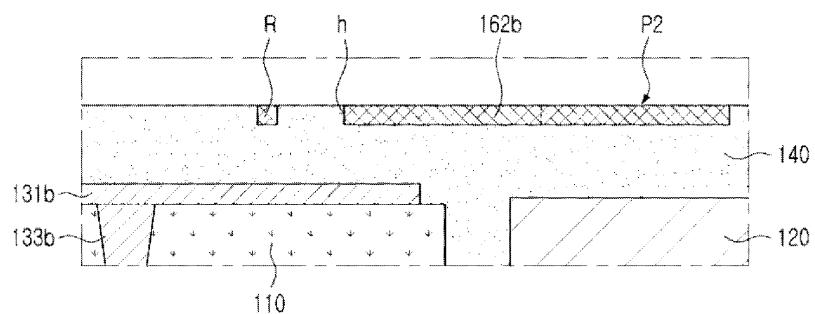

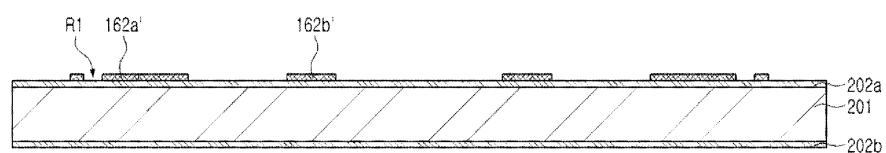

圖 15A 及圖 15B 分別為說明於圖 12F 所繪示的重佈線層的區域(A 部分)的剖面圖及平面圖。

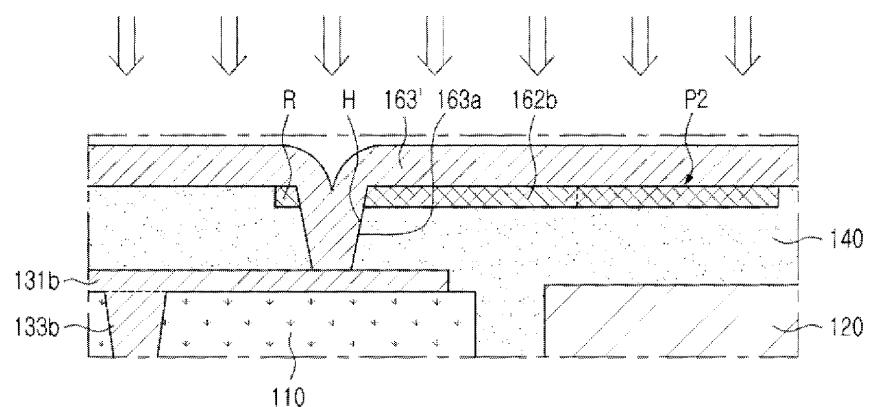

圖 16A 及圖 16B 分別為說明於圖 13B 所繪示的重佈線層的區域(A 部分)的剖面圖及平面圖。

圖 17 及圖 18 分別為說明於圖 13C 及圖 13D 所繪示的重佈線層的區域(A 部分)的剖面圖。

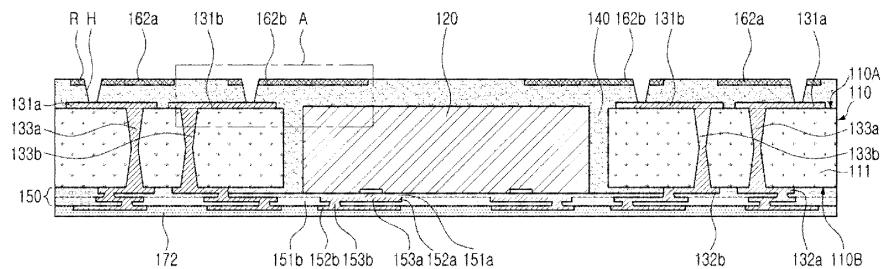

圖 19 為說明根據本揭露的另一例示性實施例的扇出型半導體封裝的側視剖面圖。

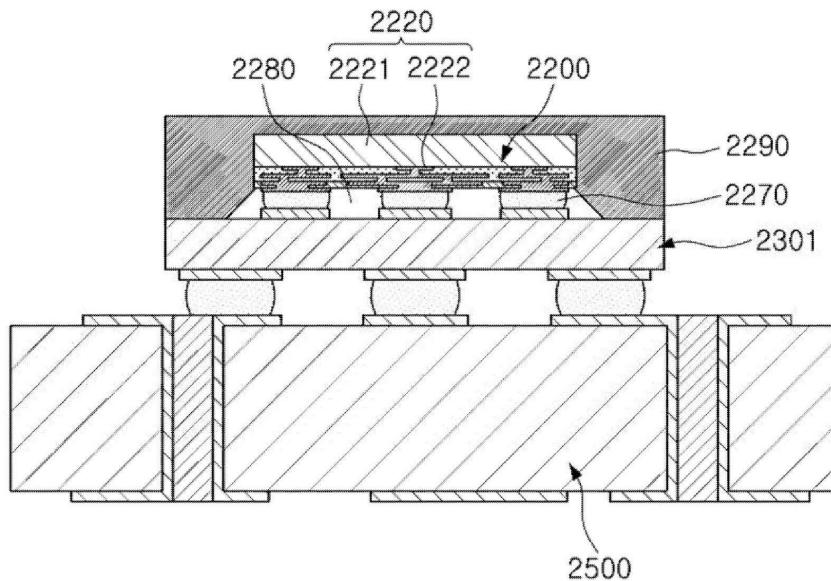

圖 20A 及圖 20B 為說明製造於圖 19 所繪示的扇出型半導體封裝的方法的形成第二重佈線層的製程的剖面圖。

圖 21A 到圖 21G 炳說明製造於圖 19 所繪示的扇出型半導體封裝的方法的製程的剖面圖。

【圖1】

【圖2】

(6)

【圖3A】

(7)

【圖3B】

【圖4】

(9)

【圖5】

【圖6】

(10)

【圖7】

【圖8】

(11)

【圖9】

【圖10A】

(12)

【圖10B】

II-II'

【圖11A】

(13)

【圖11B】

【圖12A】

【圖12B】

(14)

【圖12C】

【圖12D】

【圖12E】

(15)

【圖12F】

【圖12G】

【圖12H】

【圖13A】

【圖13B】

【圖13C】

(17)

【圖13D】

【圖14】

II-II'

【圖15A】

(18)

【圖15B】

II-II'

【圖16A】

【圖16B】

(19)

II-II'

【圖17】

II-II'

【圖18】

(20)

【圖19】

【圖20A】

(21)

【圖20B】

【圖21A】

【圖21B】

【圖21C】

【圖21D】

【圖21E】

【圖21F】

【圖21G】