【11】證書號數：I661515

【45】公告日：中華民國 108 (2019) 年 06 月 01 日

【51】Int. Cl. : H01L23/02 (2006.01)

H01L23/522 (2006.01)

發明

全 14 頁

## 【54】名稱：晶圓級封裝及方法

## WAFER LEVEL PACKAGE AND METHOD

【21】申請案號：106129936

【22】申請日：中華民國 106 (2017) 年 09 月 01 日

【11】公開編號：201814842

【43】公開日期：中華民國 107 (2018) 年 04 月 16 日

【30】優先權：2016/09/23

美國 62/399,111

2017/08/01

美國 15/666,309

【72】發明人：邱喬治(US) CHU, GEORGE

【71】申請人：美商微晶片科技公司

MICROCHIP TECHNOLOGY

INCORPORATED

美國

【74】代理人：陳長文

【56】參考文獻：

US 2012/0061823A1

US 2014/0319695A1

US 2016/0254221A1

審查人員：修宇鋒

## 【57】申請專利範圍

1. 一種形成一銅柱凸塊(pillar bump)半導體封裝之方法，其包括：提供包括一半導體基板之一已完成半導體晶圓，該半導體基板在其上經形成有覆蓋該半導體基板之一頂部表面且曝露一鋸墊之一鈍化層；在該半導體晶圓上形成一第一有機絕緣層；圖案化該第一有機絕緣層，以覆蓋該鋸墊與該鈍化層之一介面處之一第一區域，以覆蓋將形成之一凸塊墊之一第二區域，且以沿著從該鋸墊至該凸塊墊之將形成之一重佈層之路徑形成該第一有機絕緣層之島狀物，該第一有機絕緣層係從該鋸墊且係從該第一區域、該第二區域及第一有機絕緣層之該等島狀物外部該半導體晶圓之剩餘區域移除；在該第一有機絕緣層及該半導體晶圓上形成一第一晶種金屬層；在該半導體晶圓上該鋸墊及該第一有機絕緣層上方形成該重佈層，該重佈層經形成以包含與該鋸墊間隔開之該凸塊墊及將該鋸墊連接至該凸塊墊之一導電跡線，該凸塊墊係形成於該第一有機絕緣層之該第二區域上方，且該導電跡線係形成於該第一有機絕緣層之該等島狀物上方；移除不是形成於該重佈層下方之該第一晶種金屬層；在該重佈層及該半導體晶圓上形成一第二晶種金屬層；在該第二晶種金屬層上及該凸塊墊上方形成一銅柱凸塊；移除不是形成於該銅柱凸塊下方之該第二晶種金屬層；及回鋸該銅柱凸塊。

2. 如請求項 1 之方法，其中在該半導體晶圓上形成該第一有機絕緣層包括：在該半導體晶圓上形成該第一有機絕緣層，該第一有機絕緣層包括一薄膜聚合物材料。

3. 如請求項 2 之方法，其中該第一有機絕緣層包括聚醯亞胺(PI)或聚苯并噁唑(PBO)。

4. 如請求項 1 之方法，其中圖案化該第一有機絕緣層以覆蓋在該鋸墊與該鈍化層之該介面處之該第一區域包括：圖案化該第一有機絕緣層，以覆蓋該鋸墊與該鈍化層之該介面處之該第一區域，該第一有機絕緣層憑藉一重疊寬度與該介面重疊，該第一有機絕緣層係從該鋸墊且係從該第一區域、該第二區域及第一有機絕緣層之該等島狀物外部該半導體晶圓之該剩餘區域移除。

5. 如請求項 4 之方法，其中圖案化該第一有機絕緣層以覆蓋在該鋸墊與該鈍化層之該介面處之該第一區域包括：將該第一有機絕緣層圖案化為一圓形，以覆蓋該鋸墊與該鈍化層之該介面處之該第一區域，該第一有機絕緣層憑藉一重疊寬度與該介面重疊，該第一有機絕緣層係從該鋸墊且係從該第一區域、該第二區域及第一有機絕緣層之該等島狀物外部該半導體晶圓之該剩餘區域移除。

6. 如請求項 4 之方法，其中圖案化該第一有機絕緣層以覆蓋在該鋸墊與該鈍化層之該介面處之該區域包括：將該第一有機絕緣層圖案化為一矩形，以覆蓋該鋸墊與該鈍化層之該介面處之該第一區域，該第一有機絕緣層憑藉一重疊寬度與該介面重疊，該第一有機絕緣層係從該鋸墊且係從該第一區域、該第二區域及第一有機絕緣層之該等島狀物外部該半導體晶圓之該剩餘區域移除。

7. 如請求項 1 之方法，其中在該半導體晶圓上形成該第一有機絕緣層且圖案化該第一有機絕緣層包括：形成該第一有機絕緣層以覆蓋該半導體晶圓之整個表面；及圖案化該第一有機絕緣層，以從除在該鋸墊與該鈍化層之該介面處之該第一區域、將形成之該凸塊墊之該第二區域，及該第一有機絕緣層之該等島狀物外之該半導體晶圓之該表面移除該有機絕緣層。

8. 如請求項 1 之方法，其中在該半導體晶圓上形成該重佈層包括：圖案化該半導體晶圓以曝露將形成該重佈層之區域；及藉由電鍍，在該等曝露區域中形成一銅層作為該半導體晶圓上之該重佈層。

9. 如請求項 1 之方法，進一步包括：在移除該第一晶種金屬層之後，且在形成該第二晶種金屬層之前，在該半導體晶圓上該重佈層上方形成一第二有機絕緣層；及圖案化該第二有機絕緣層，以覆蓋該鋸墊上方及周圍之一第三區域，以覆蓋該凸塊墊周圍之一第四區域，且以沿著從該鋸墊至該凸塊墊之該重佈層之該路徑形成該第二有機絕緣層之島狀物，該第二有機絕緣層係從該凸塊墊且係從該第三區域及該第四區域外部該半導體晶圓之剩餘區域移除，其中在該半導體晶圓上，於藉由該重佈層及該第二有機絕緣層形成之該凸塊墊上方，形成該第二晶種金屬層。

10. 如請求項 9 之方法，其中該第二有機絕緣層之該等島狀物經形成從該第一有機絕緣層之該等島狀物偏移。

11. 如請求項 9 之方法，其中在該半導體晶圓上該重佈層上方形成該第二有機絕緣層包括：在該半導體晶圓上該重佈層上方形成該第二有機絕緣層，該第二有機絕緣層包括一薄膜聚合物材料。

12. 如請求項 11 之方法，其中該第二有機絕緣層包括聚醯亞胺(PI)或聚苯并噁唑(PBO)。

13. 如請求項 9 之方法，其中在該半導體晶圓上形成該第二有機絕緣層且圖案化該第二有機絕緣層包括：在該重佈層上方形成該第二有機絕緣層以覆蓋該半導體晶圓之整個表面；及圖案化該第二有機絕緣層，以從除該鋸墊上方及周圍之該第三區域、該凸塊墊周圍之該第四區域，及該第二有機絕緣層之該等島狀物外之該半導體晶圓之該表面移除該第二有機絕緣層。

#### 圖式簡單說明

在下文實施方式及隨附圖式中揭示本發明之多種實施例。

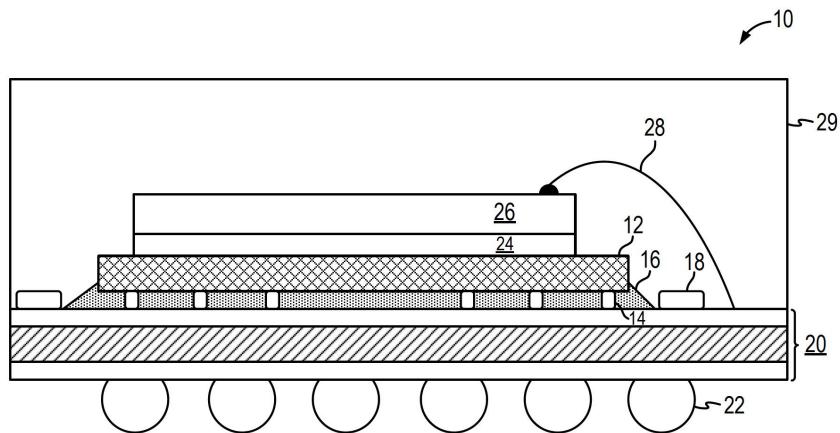

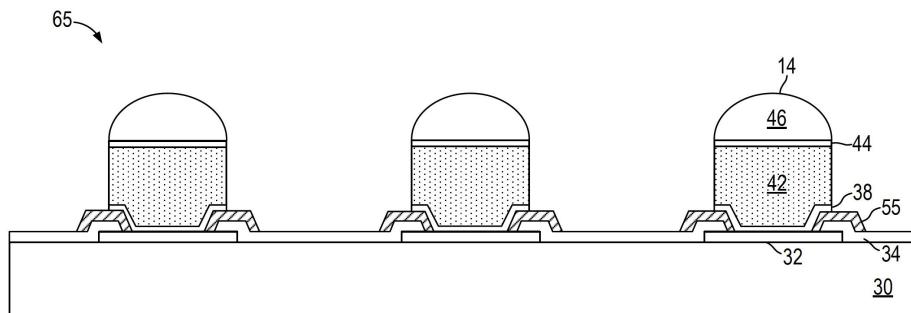

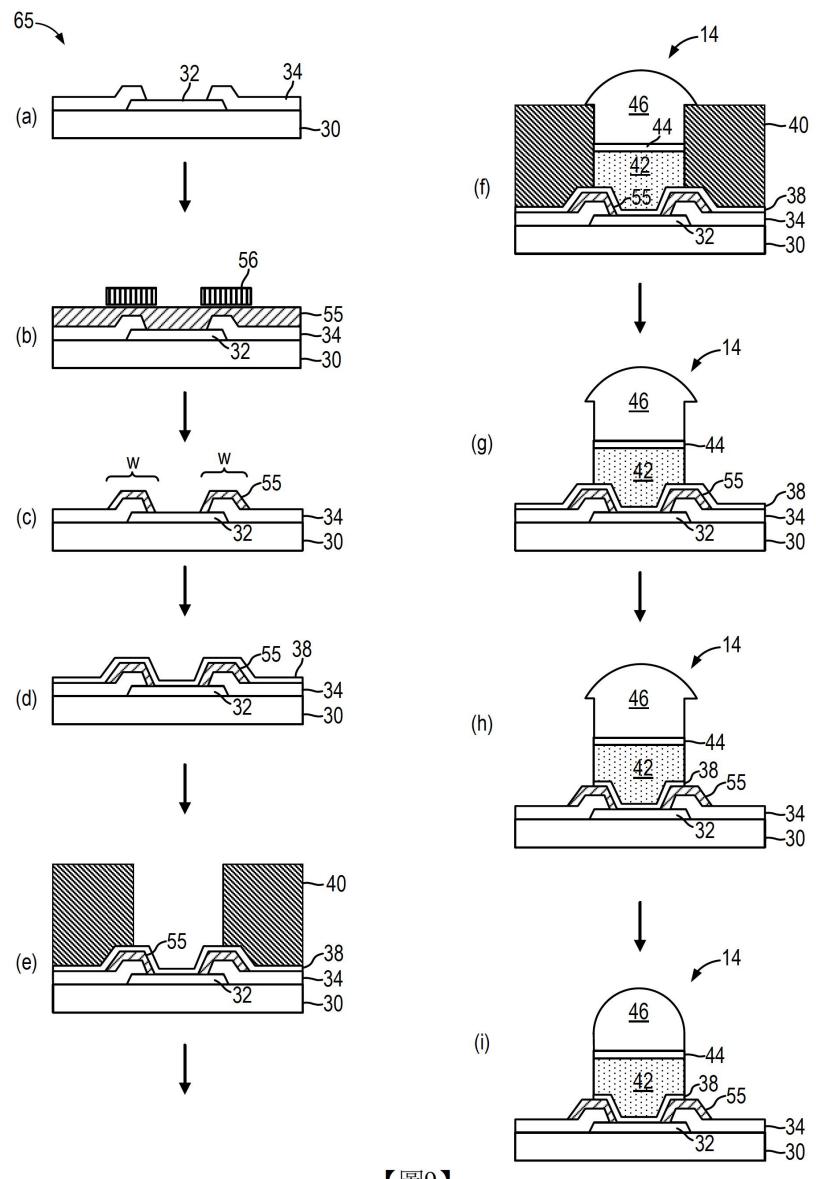

圖 1 係在一些實例中採用銅柱凸塊覆晶互連技術之一經封裝積體電路之一橫截面視圖。

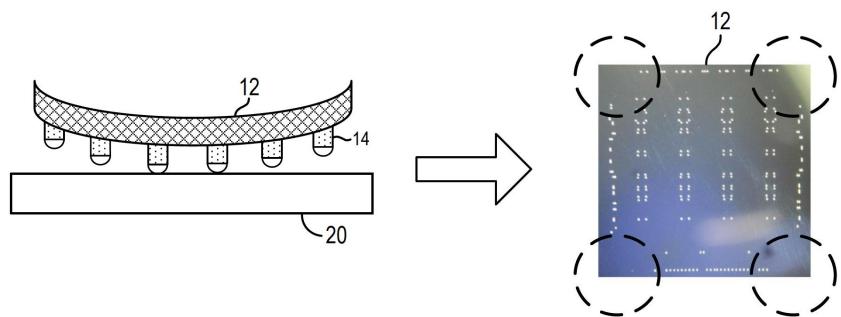

圖 2 繪示在一個實例中歸因於晶粒翹曲之一封裝失效模式。

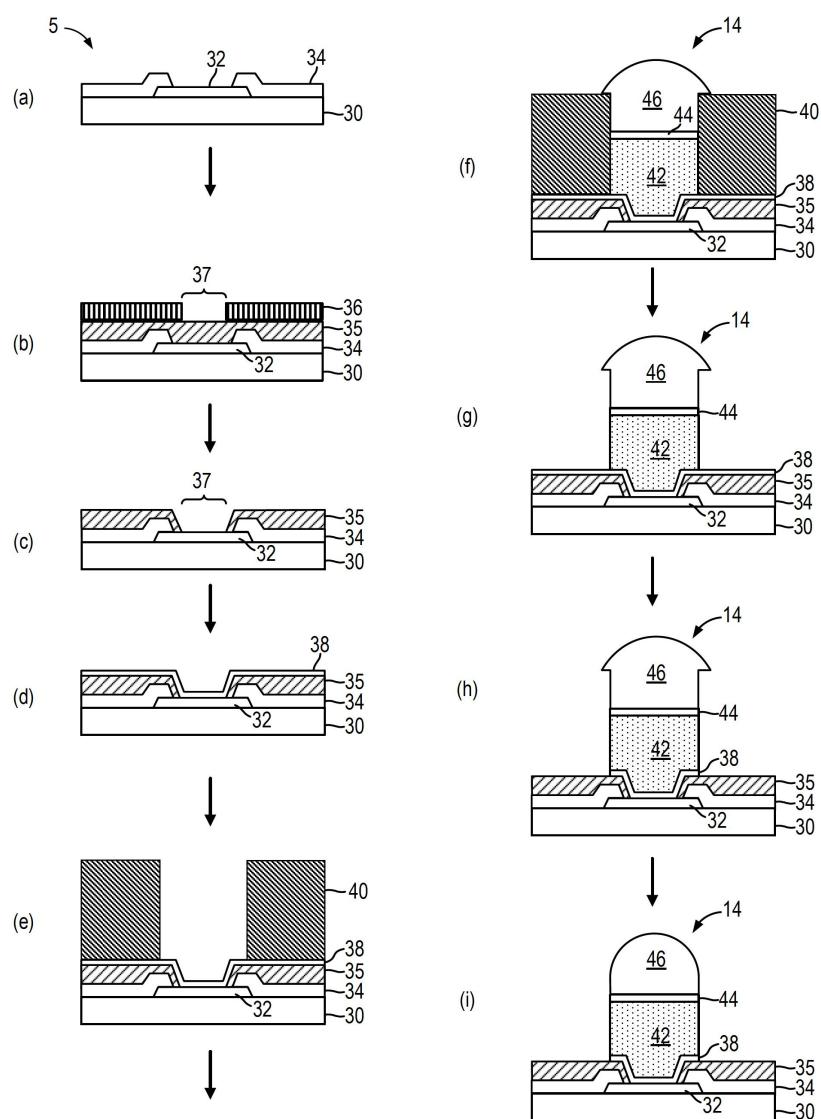

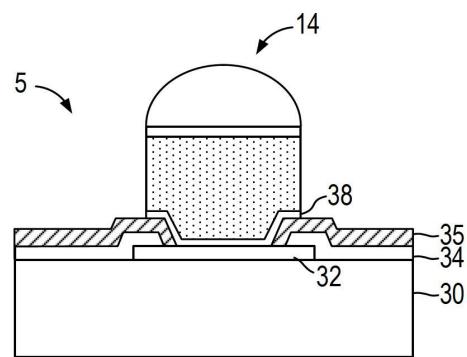

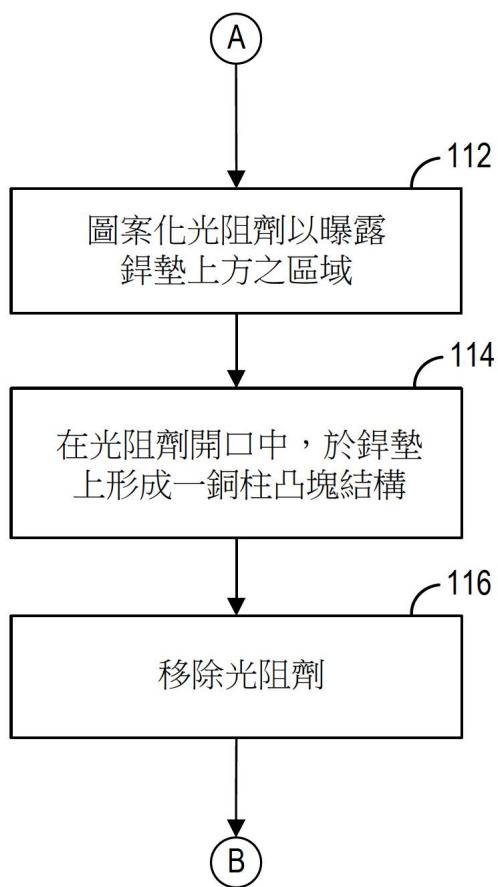

圖 3(其包含圖 3(a)至圖 3(i))繪示用於在半導體晶圓之一鋸墊上形成一銅柱凸塊之習知後端處理步驟。

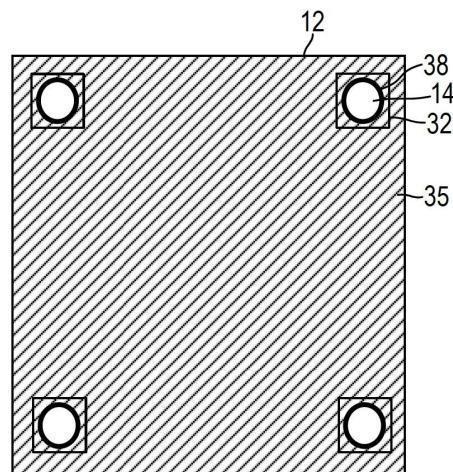

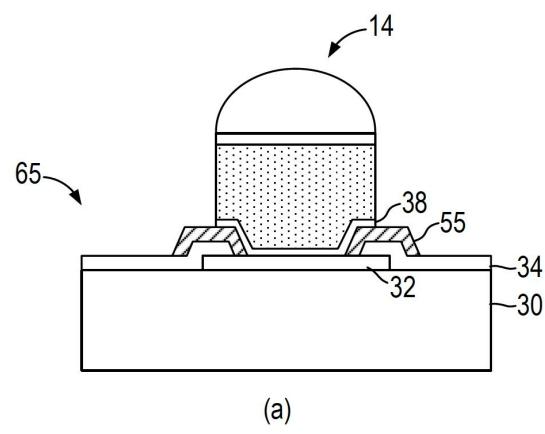

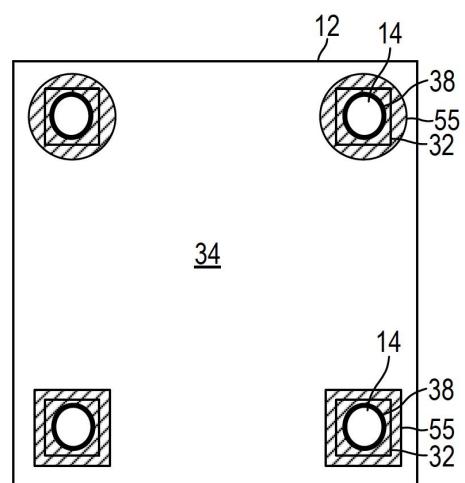

圖 4(其包含圖 4(a)及圖 4(b))係形成在一半導體晶圓上之一銅柱凸塊之一橫截面視圖及具有使用圖 3 之習知後端處理步驟形成之銅柱凸塊之一積體電路晶粒之一俯視圖。

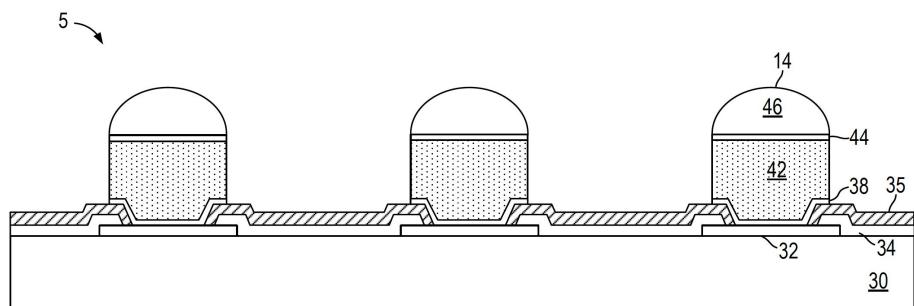

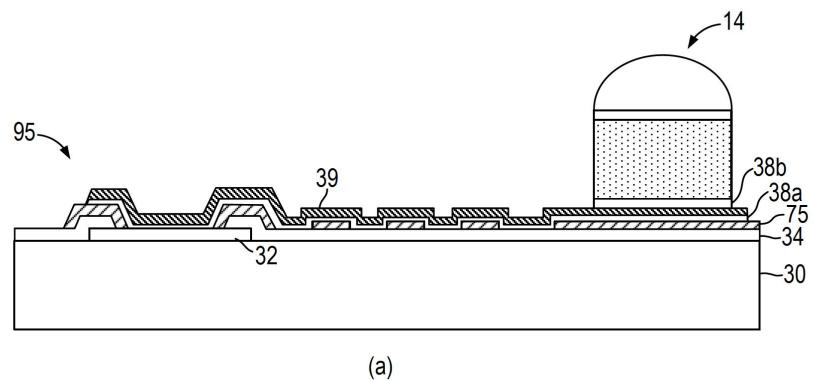

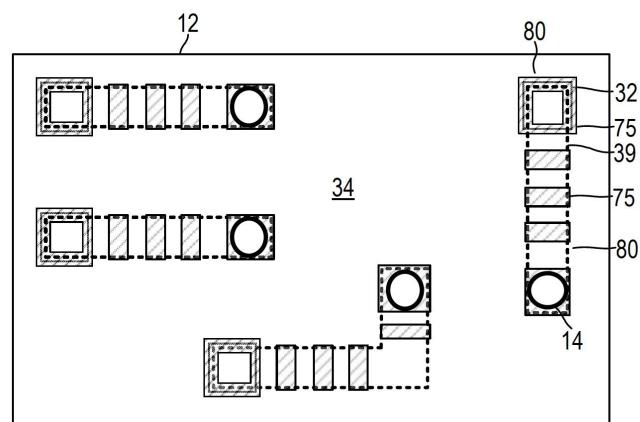

圖 5(其包含圖 5(a)及圖 5(b))係在一些實例中形成在一重佈層上之一銅柱凸塊之一橫截面視圖及具有形成於一重佈層上之銅柱凸塊之一積體電路晶粒之一俯視圖。

圖 6 係圖 3 及圖 4 中之半導體晶圓之另一橫截面視圖，其展示其上形成有多個銅柱凸塊之晶圓之一較大部分。

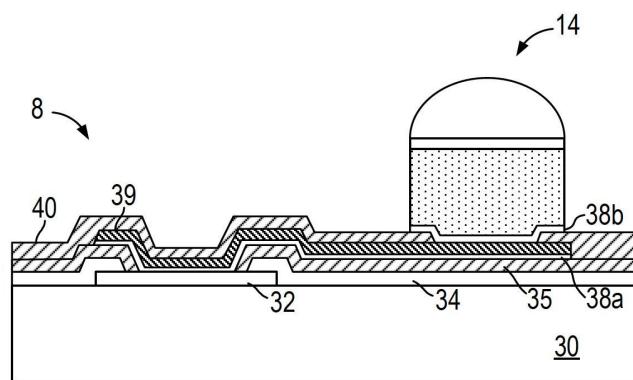

圖 7 係在本發明之實施例中具有使用半導體封裝方法形成在其上之銅柱凸塊之一半導體晶圓之一橫截面視圖。

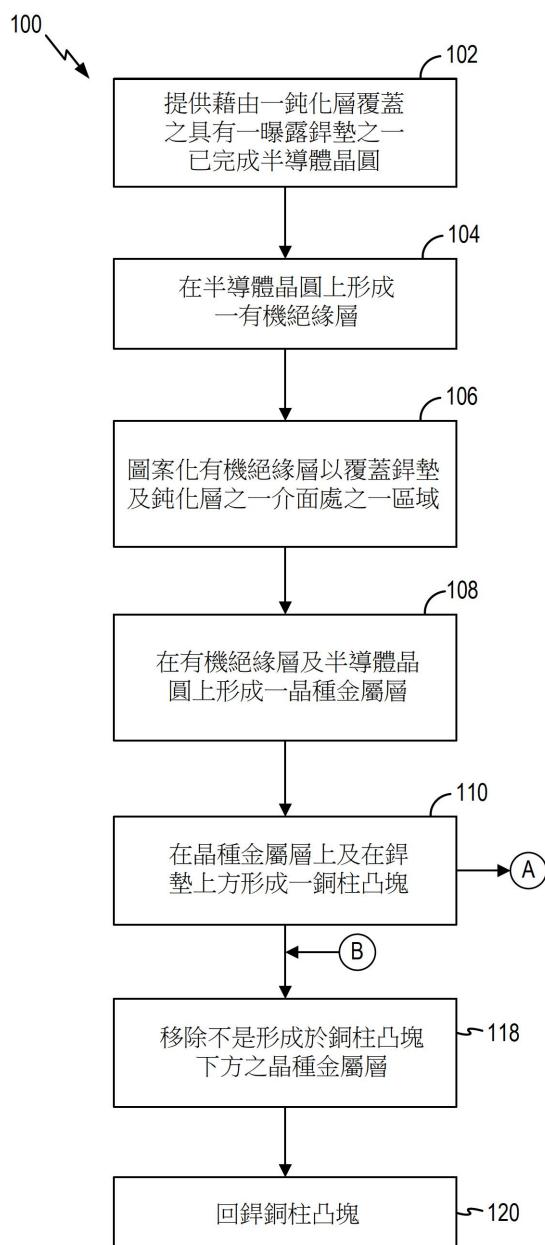

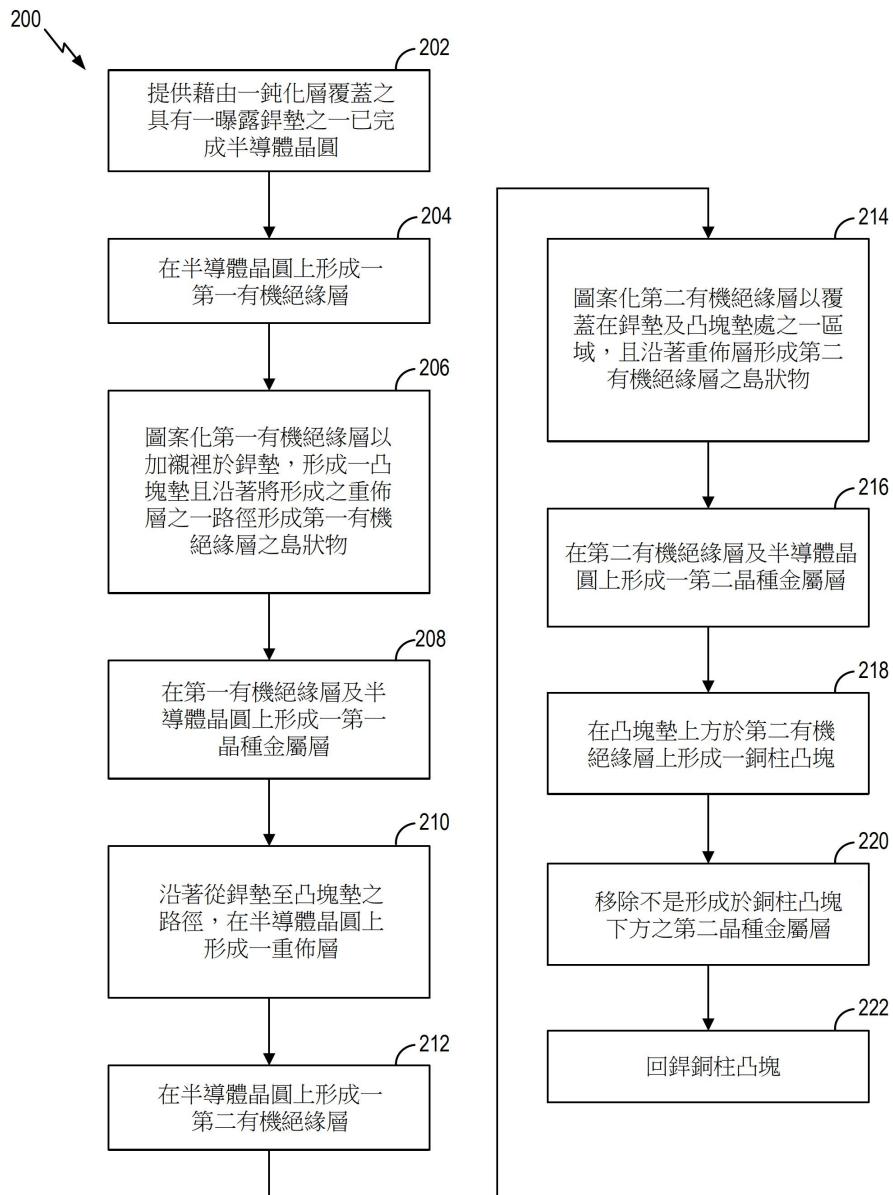

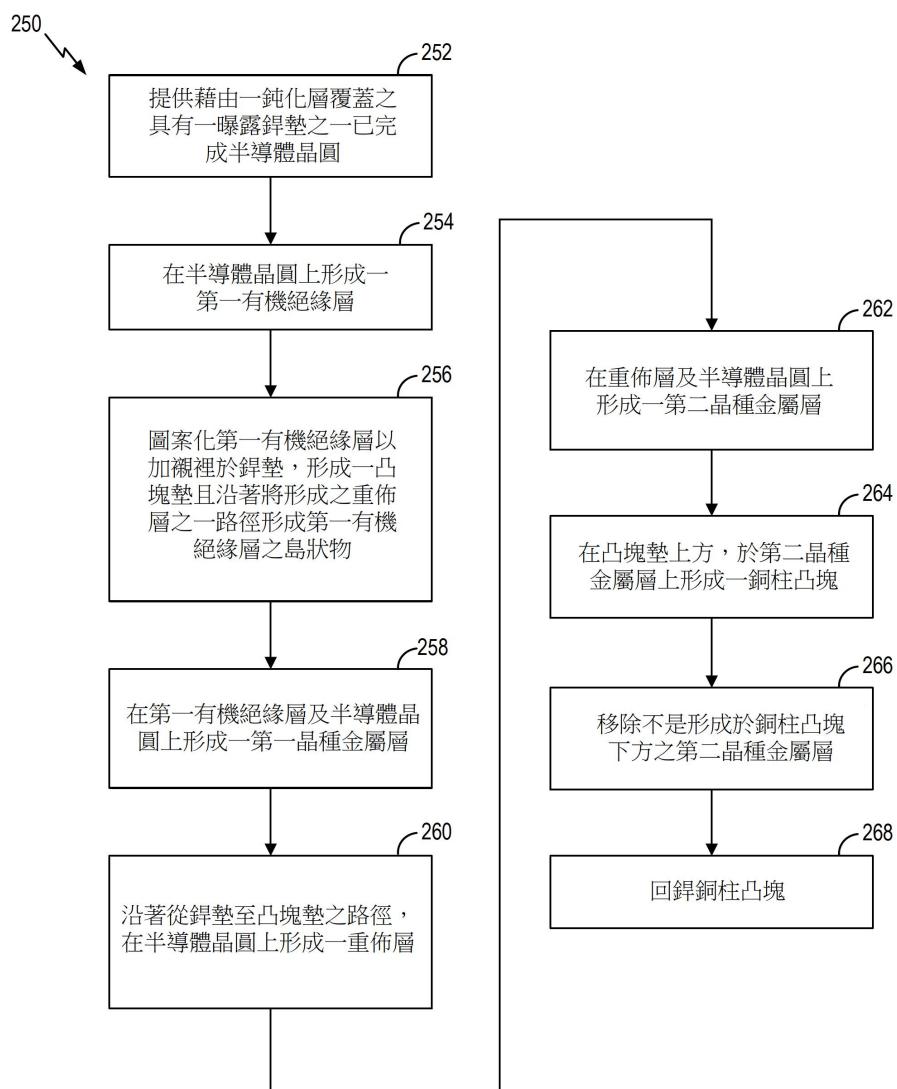

圖 8(其包含圖 8(a))係繪示在本發明之實施例中用於形成銅柱凸塊之半導體封裝方法之一流程圖。

圖 9(其包含圖 9(a)至圖 9(i))繪示用於使用圖 8 中之半導體封裝方法在半導體晶圓之一鋅墊上形成一銅柱凸塊之後端處理步驟。

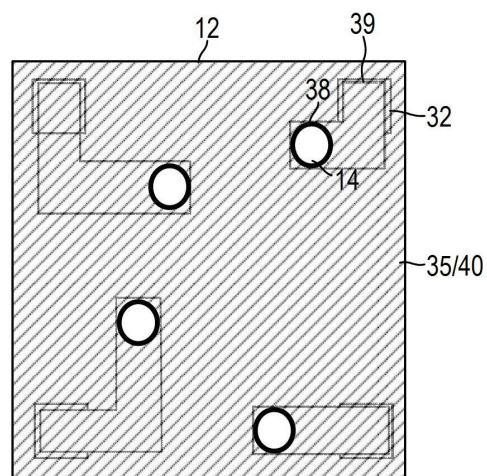

圖 10(其包含圖 10(a)及圖 10(b))係形成在一半導體晶圓上之一銅柱凸塊之一橫截面視圖及具有使用圖 8 之後端半導體封裝方法形成之銅柱凸塊之一積體電路晶粒之一俯視圖。

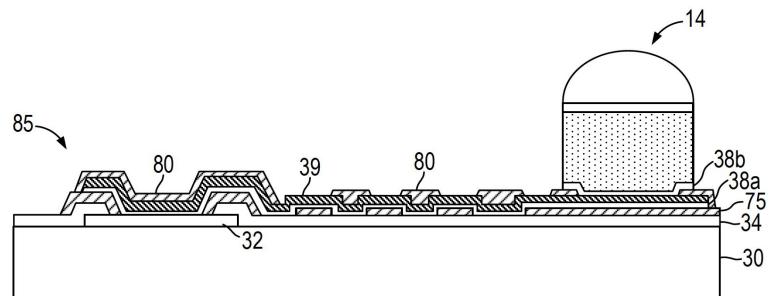

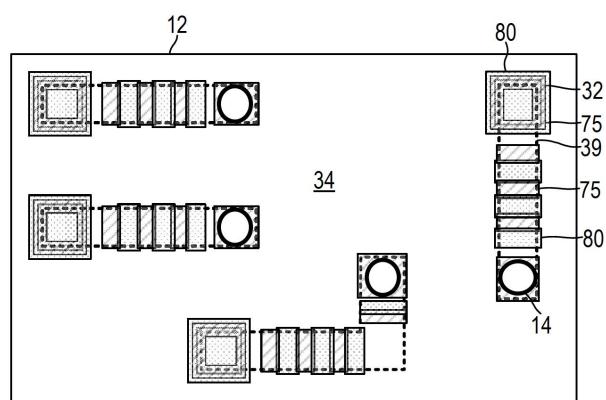

圖 11(其包含圖 11(a)及圖 11(b))係在本發明之一項實施例中使用一重佈層之一銅柱凸塊之一橫截面視圖及使用半導體封裝方法形成之一積體電路晶粒之一俯視圖。

圖 12(其包含圖 12(a)及圖 12(b))係在本發明之一替代實施例中使用一重佈層之一銅柱凸塊之一橫截面視圖及使用半導體封裝方法形成之一積體電路晶粒之一俯視圖。

圖 13 係繪示在本發明之實施例中用於使用一重佈層形成銅柱凸塊之半導體封裝方法之一流程圖。

圖 14 係繪示在本發明之實施例中用於使用一重佈層形成銅柱凸塊之半導體封裝方法之一流程圖。

【圖1】

(4)

【圖2】

【圖3】

(5)

(a)

(b)

【圖4】

(6)

(a)

(b)

【圖5】

【圖6】

(7)

【圖7】

【圖8】

【圖8(a)】

【圖9】

(10)

(a)

(b)

【圖10】

(11)

(a)

(b)

【圖11】

(12)

(a)

(b)

【圖12】

【圖13】

【圖14】