【11】證書號數：I667947

【45】公告日：中華民國 108 (2019) 年 08 月 01 日

【51】Int. Cl. : H05K1/09 (2006.01) B32B15/08 (2006.01)

發明

全 7 頁

【54】名稱：粗化銅箔、被銅積層板及印刷電路板

【21】申請案號：103124279 【22】申請日：中華民國 103 (2014) 年 07 月 15 日

【11】公開編號：201505494 【43】公開日期：中華民國 104 (2015) 年 02 月 01 日

【30】優先權：2013/07/30 日本 2013-158039

【72】發明人：堀口賢 (JP) HORIGUCHI, KEN；室賀岳海 (JP) MUROGA, TAKEMI；後藤千鶴 (JP) GOTO, CHIZURU；小平宗男 (JP) KODAIRA, MUNEO

【71】申請人：J X 金屬股份有限公司 JX NIPPON MINING &amp; METALS CORPORATION

日本

【74】代理人：侯德銘

【56】參考文獻：

JP 2006-179537A

JP 2011-9267A

審查人員：劉育瑜

## 【57】申請專利範圍

1. 一種粗化銅箔，係為使用於傳送高頻電訊號的印刷電路板的粗化銅箔，具備：基材，由銅箔或銅合金箔製成；以及電鍍層，具有成長在前述基材的至少任一主面上的基底電鍍層和成長在前述基底電鍍層上的粗化電鍍層，其中最終退火處理後的前述基材的電鍍層成長面，利用 X 線繞射分析法進行測量時，若將 X 線對前述電鍍層成長面的入射角度設為  $\theta$ ，以  $2\theta/\theta$  法測量所得之立方纖構的峰值強度比設為 A，以  $\omega$  掃描測量所得之前述立方纖構的搖擺曲線的半寬高與積分寬度之比的面外配向比設為 B，從以  $\Phi$  掃描所得極點圖算出之前述立方纖構的半寬高與積分寬度之比的面內配向比設為 C 時，係為以 A 與 B 與 C 之積表示的前述立方纖構的總和配向率為 80% 以上的面，而前述電訊號的頻率設為  $f[\text{GHz}]$  時，前述電鍍層的厚度為  $0.4\mu\text{m}$  以上  $6.3/(f)^{1/2}\mu\text{m}$  以下；前述電鍍層表面的十點平均粗度( $R_z$ )為  $0.6\mu\text{m}$  以上  $1.2\mu\text{m}$  以下。

2. 如申請專利範圍第 1 項所述的粗化銅箔，其中，前述電鍍層表面的十點平均粗度( $R_z$ )為  $0.6\mu\text{m}$  以上  $0.8\mu\text{m}$  以下。

3. 一種粗化銅箔，係為使用於傳送高頻電訊號的印刷電路板的粗化銅箔，具備：基材，由銅箔或銅合金箔製成；以及電鍍層，具有成長在前述基材的至少任一主面上的基底電鍍層和成長在前述基底電鍍層上的粗化電鍍層，其中最終退火處理後的前述基材的電鍍層成長面，利用 X 線繞射分析法進行測量時，若將 X 線對前述電鍍層成長面的入射角度設為  $\theta$ ，以  $2\theta/\theta$  法測量所得之立方纖構的峰值強度比設為 A，以  $\omega$  掃描測量所得之前述立方纖構的搖擺曲線的半寬高與積分寬度之比的面外配向比設為 B，從以  $\Phi$  掃描所得極點圖算出之前述立方纖構的半寬高與積分寬度之比的面內配向比設為 C 時，係為以 A 與 B 與 C 之積表示的前述立方纖構的總和配向率為 50% 以上的面，而前述電訊號的頻率設為  $f[\text{GHz}]$  時，前述電鍍層的厚度為  $0.4\mu\text{m}$  以上  $6.3/(f)^{1/2}\mu\text{m}$  以下；前述電鍍層表面的十點平均粗度( $R_z$ )為  $0.6\mu\text{m}$  以上  $0.8\mu\text{m}$  以下。

4. 如申請專利範圍第 1 項至第 3 項中任一項所述的粗化銅箔，其中，前述基底電鍍層係使用含有機硫化物的電鍍液所形成。

5. 一種被銅積層板，具備：申請專利範圍第 1 項至第 4 項中任一項所述的粗化銅箔；以及以與前述粗化銅箔的電鍍層成長面相接的方式設置的樹脂層。

6. 一種印刷電路板，係使用申請專利範圍第 5 項所述的被銅積層板來形成。

#### 圖式簡單說明

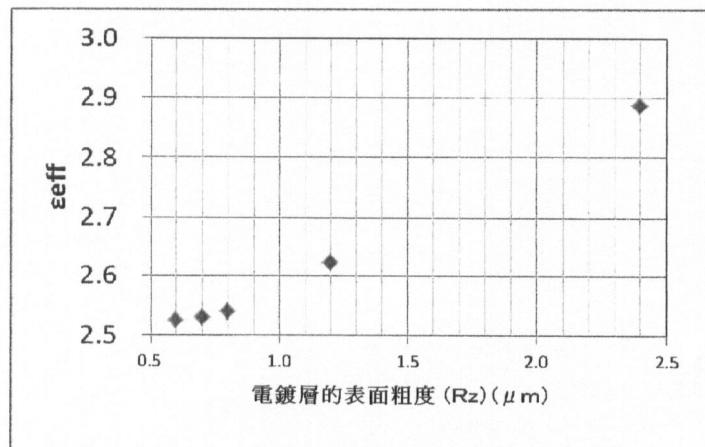

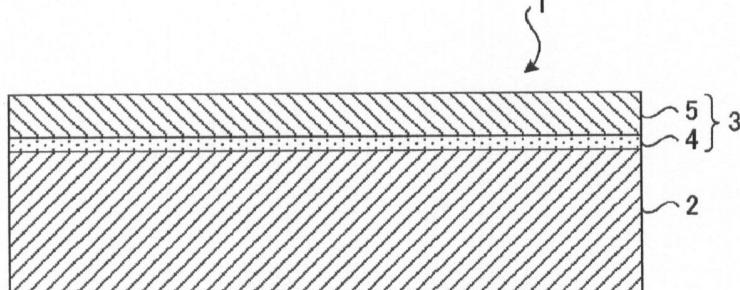

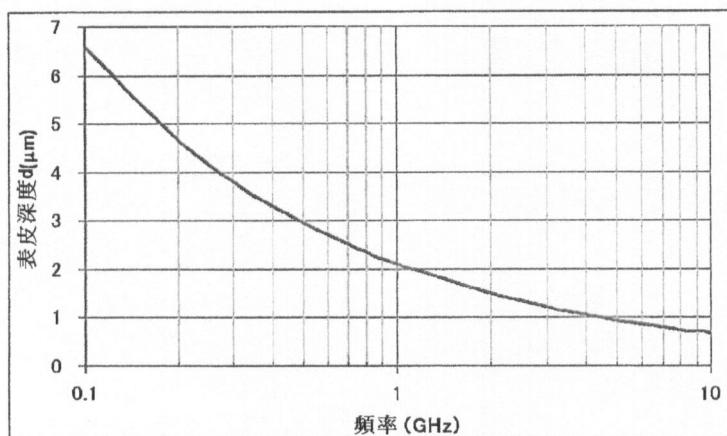

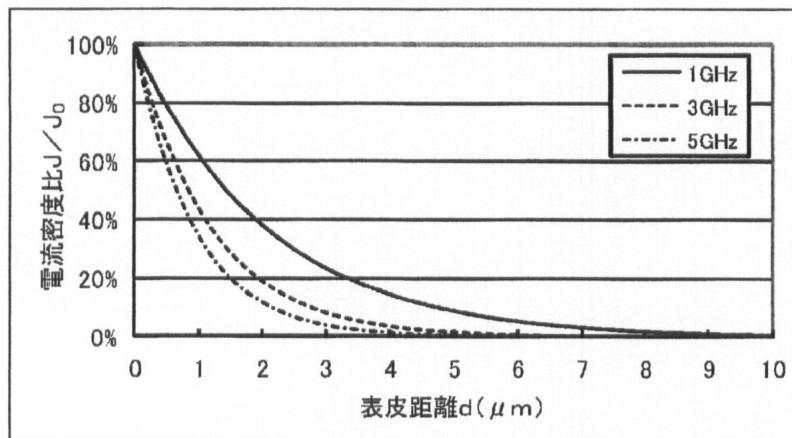

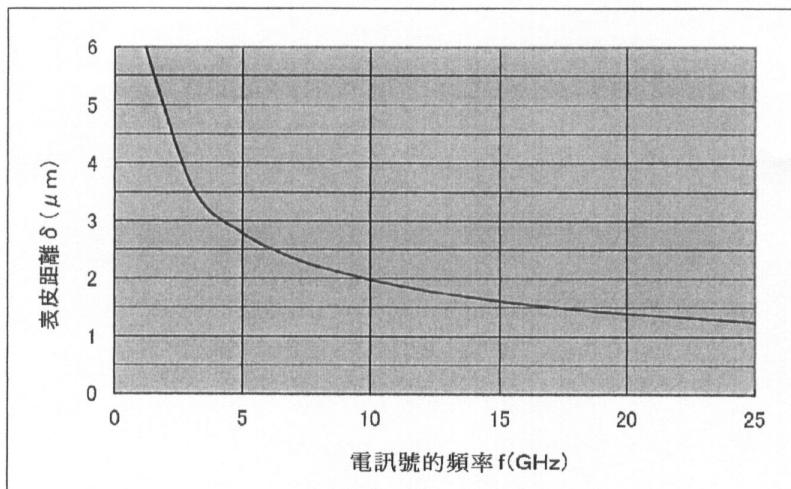

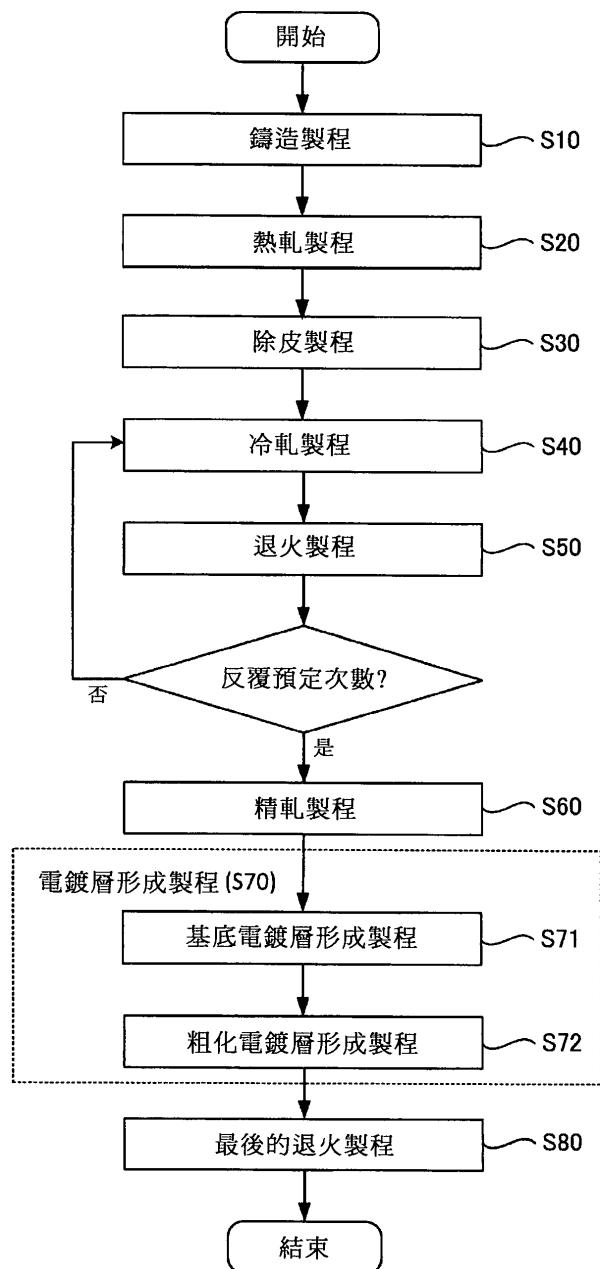

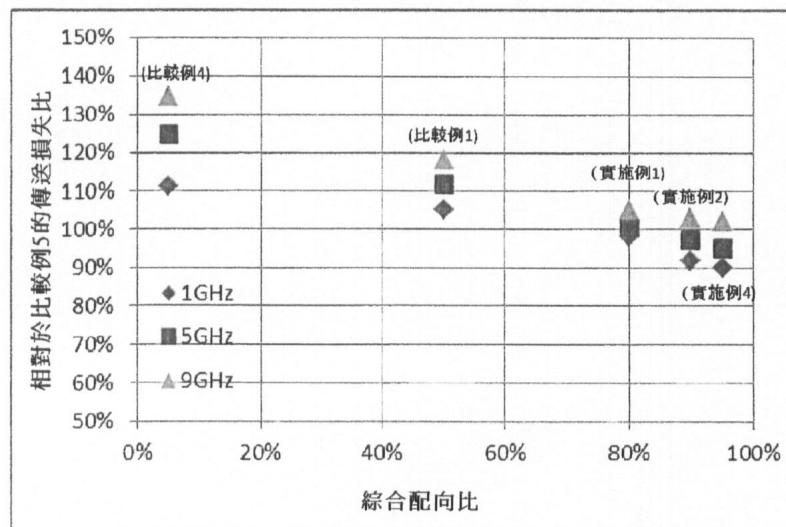

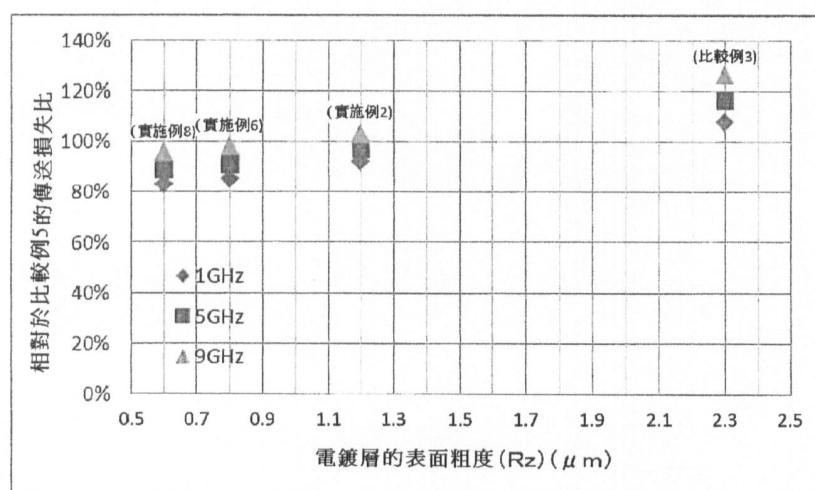

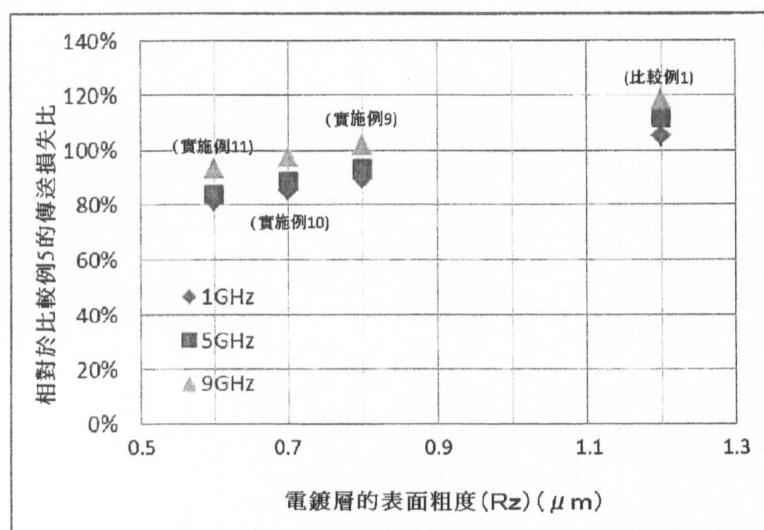

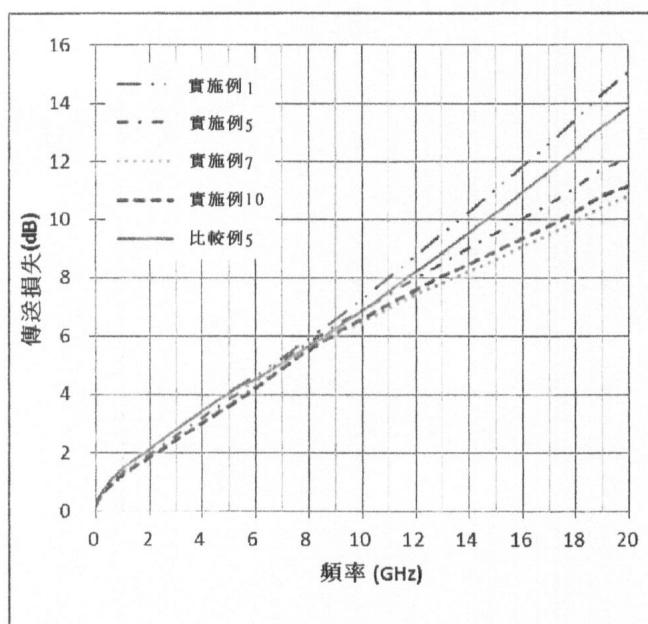

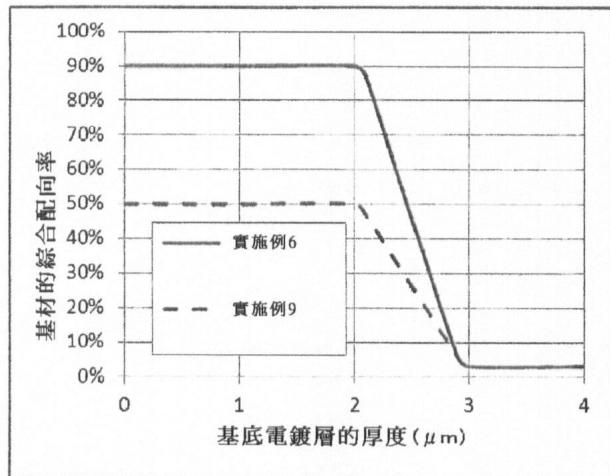

第 1 圖為本發明一實施形態之粗化銅箔的示意剖面圖；第 2 圖為顯示本發明一實施形態之粗化銅箔所傳送的電訊號的頻率與表皮深度之關係的曲線圖；第 3 圖為顯示本發明一實施形態之粗化銅箔所傳送的電訊號的表皮距離與電流密度比之關係的曲線圖；第 4 圖為顯示本發明一實施形態之粗化銅箔所傳送的電訊號的頻率與表皮距離之關係的曲線圖；第 5 圖為顯示本發明一實施形態之粗化銅箔的製程流程圖；第 6 圖為顯示本發明一實施例之基材的綜合配向率與傳送損失之關係的曲線圖；第 7 圖為顯示本發明一實施例之粗化電鍍層的表面粗度( $R_z$ )與傳送損失之關係的曲線圖；第 8 圖為顯示本發明一實施例之粗化電鍍層的表面粗度( $R_z$ )與傳送損失之關係的曲線圖；第 9 圖為顯示本發明一實施例的電訊號頻率與傳送損失之關係的曲線圖；第 10 圖為顯示發明一實施例之基材的綜合配向率與基底電鍍層厚度之關係的曲線圖；以及第 11 圖為顯示本發明一實施例之實效比介電常數與電鍍層的表面粗度( $R_z$ )之關係的曲線圖。

第1圖

第2圖

(3)

第3圖

第4圖

第5圖

第6圖

第7圖

(6)

第8圖

第9圖

(7)

第10圖

第11圖