【11】證書號數：I665585

【45】公告日：中華民國 108 (2019) 年 07 月 11 日

|                |                            |                             |

|----------------|----------------------------|-----------------------------|

| 【51】Int. Cl. : | <i>G06F3/02 (2006.01)</i>  | <i>H01H13/70 (2006.01)</i>  |

|                | <i>G06F3/023 (2006.01)</i> | <i>G06F3/0488 (2013.01)</i> |

發明

全 9 頁

## 【54】名稱：鍵盤

KEYBOARD

【21】申請案號：107137596

【22】申請日：中華民國 107 (2018) 年 10 月 24 日

【30】優先權：2018/10/04

美國 62/740,963

【72】發明人：陳志豪 (TW) CHEN, CHIH-HAO；崛內光雄 (JP) HORIUCHI, MITSUO

【71】申請人：群光電子股份有限公司 CHICONY ELECTRONICS CO., LTD.

新北市三重區光復路二段 69 號

【74】代理人：陳啟桐；廖和信

## 【56】參考文獻：

TW I523057

TW M528009

TW M564194

US 8247714B2

US 2017/0294278A1

審查人員：陳泰龍

## 【57】申請專利範圍

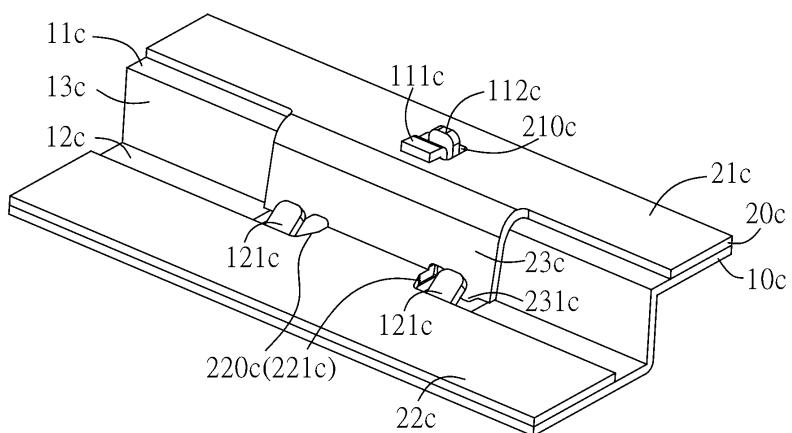

1. 一種鍵盤，包括：一底板，包括：一第一部分，具有至少一第一限位部及至少一第二限位部；一第二部分，與該第一部分相互平行，該第二部分具有至少一第三限位部，該第三限位部自該第二部分凸起；及一斜面部分，連接該第一部分與該第二部分；以及一薄膜電路板，設置於該底板，該薄膜電路板包括：一第一區塊，位於該第一部分，且該第一區塊具有至少一開口，該第一限位部及該第二限位部容置於該至少一開口內，該第一限位部限制該第一區塊往一第一方向移動，該第二限位部限制該第一區塊往一第二方向移動，該第一方向相反於該第二方向；一第二區塊，位於該第二部分，且該第二區塊具有至少一開口；及至少一連接部，位於該斜面部分，該第三限位部自該第二區塊的該開口穿出並抵接於該連接部。

2. 如申請專利範圍第 1 項所述之鍵盤，其中該第一限位部及該第二限位部容置於該第一區塊的同一該開口內，且該第一限位部與該第二限位部分別抵接於該第一區塊的該開口的相對二側。

3. 如申請專利範圍第 1 項所述之鍵盤，其中該第一區塊具有複數該開口，其包括至少一第一開口及至少一第二開口，該第一限位部容置於該第一開口內，該第二限位部容置於該第二開口內。

4. 如申請專利範圍第 3 項所述之鍵盤，其中該第一開口為一封閉式開口，該第一限位部抵接於該第一開口靠近於該連接部的一側。

5. 如申請專利範圍第 3 項所述之鍵盤，其中該第二開口為朝向該連接部的一開放式開口，該第二限位部抵接於第二開口的一內側。

6. 如申請專利範圍第 1 項所述之鍵盤，其中該第一限位部為一卡勾，該卡勾的一下表面朝向該薄膜電路板之該第一區塊。

7. 如申請專利範圍第 6 項所述之鍵盤，其中該斜面部分具有一中空部，且該中空部與該卡勾的該下表面相互連通。

8. 如申請專利範圍第 7 項所述之鍵盤，其中該第一部分具有至少一延伸部，其往該第二部分的方向延伸並與該中空部相鄰，且該延伸部凸出於該斜面部分及該中空部。

9. 如申請專利範圍第 1 項所述之鍵盤，其中該第一部分具有至少一延伸部，其往該第二部分的方向延伸，且該延伸部凸出於該斜面部分。

10. 如申請專利範圍第 8 或 9 項所述之鍵盤，其中該延伸部之下表面抵接於該薄膜電路板之部分該連接部，且抵接於該連接部之一頂面。

11. 如申請專利範圍第 1 項所述之鍵盤，其中該第二限位部為自該第一部分之上表面凸起的一凸部。

12. 如申請專利範圍第 1 項所述之鍵盤，其中該第二區塊的該開口為一第三開口，且該第三開口為一開放式開口。

13. 如申請專利範圍第 1 項所述之鍵盤，其中該第三限位部自該第二部分朝向該第一部分及該斜面部分的方向延伸。

14. 如申請專利範圍第 1 項所述之鍵盤，其中該第三限位部自該第二部分之上表面凸起的一凸部。

15. 如申請專利範圍第 1 項所述之鍵盤，其中該第一部分與該第二部分具有一高度差，且該第一部分高於該第二部分。

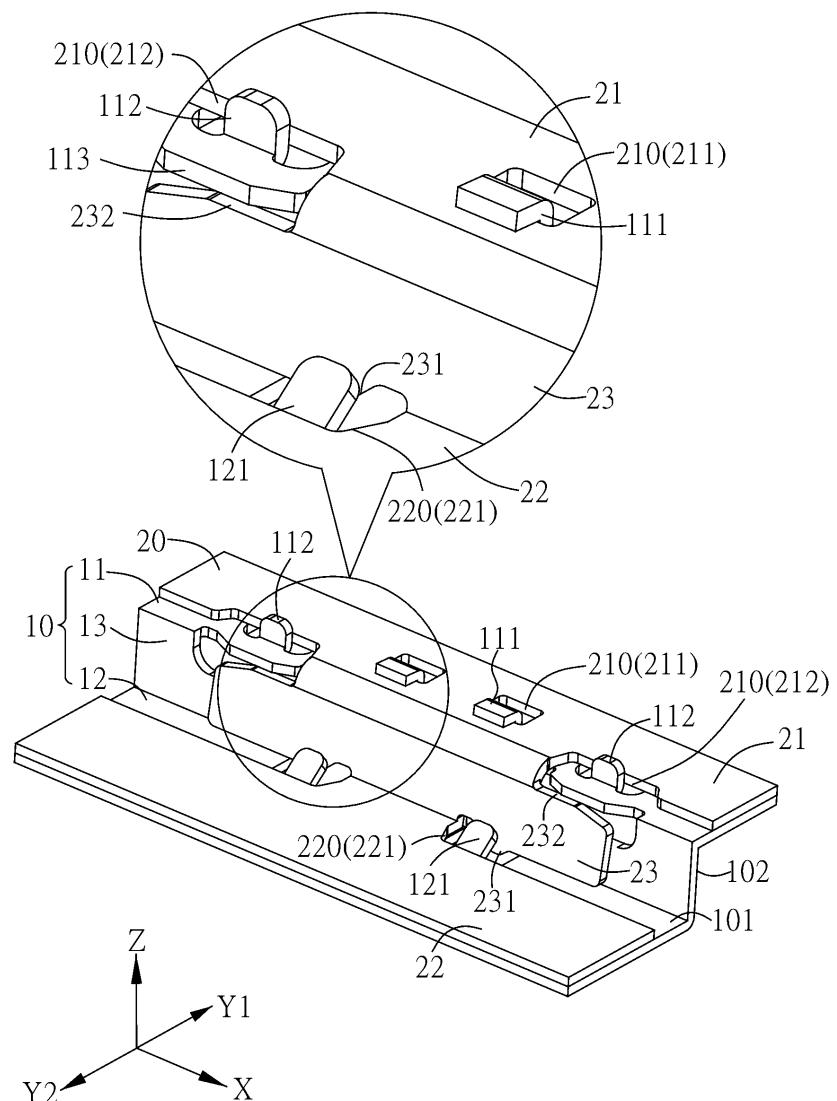

#### 圖式簡單說明

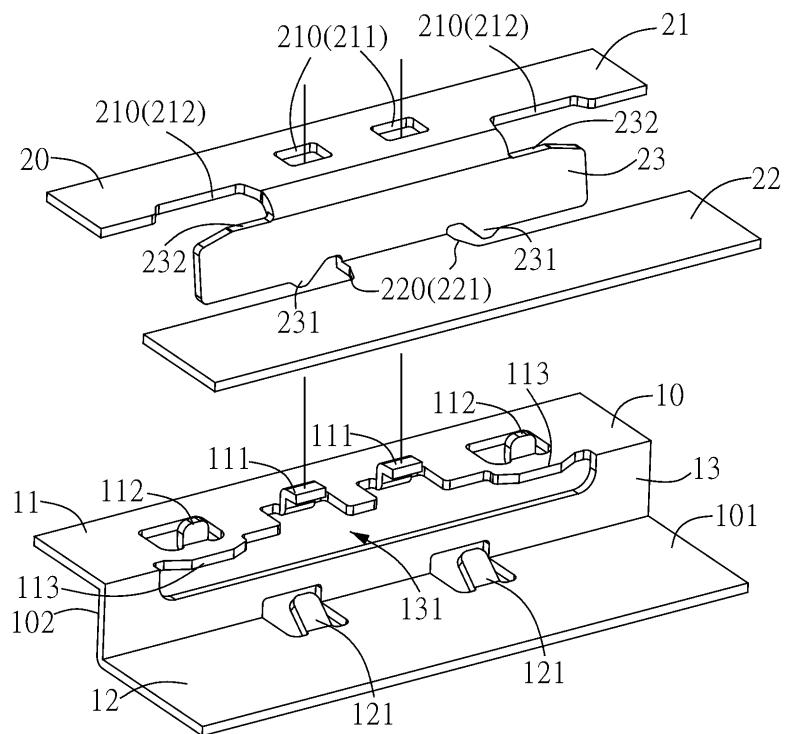

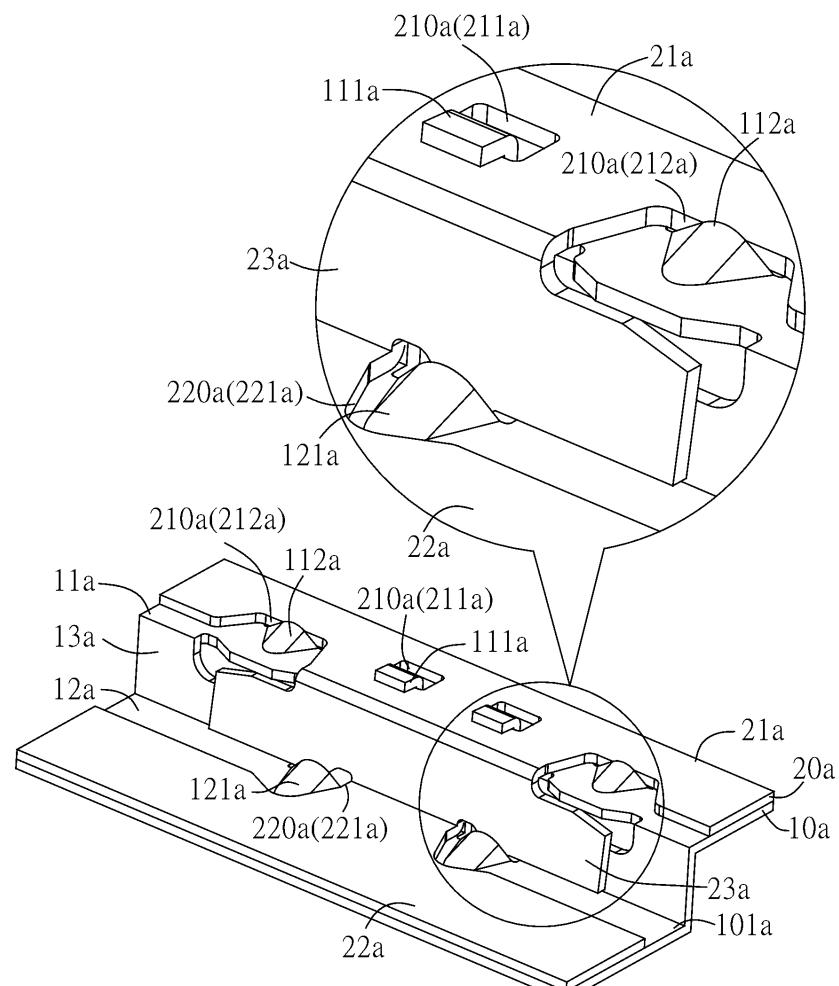

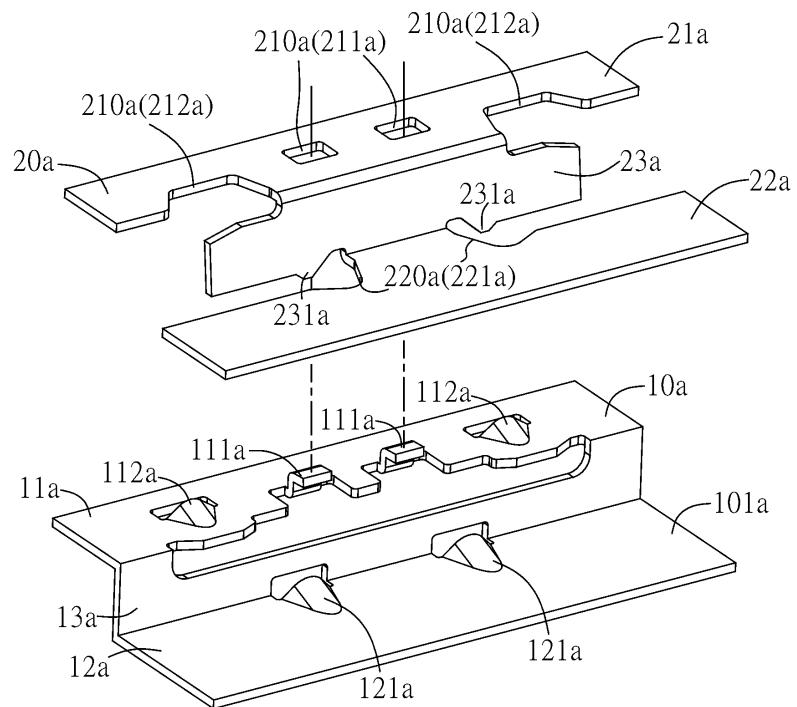

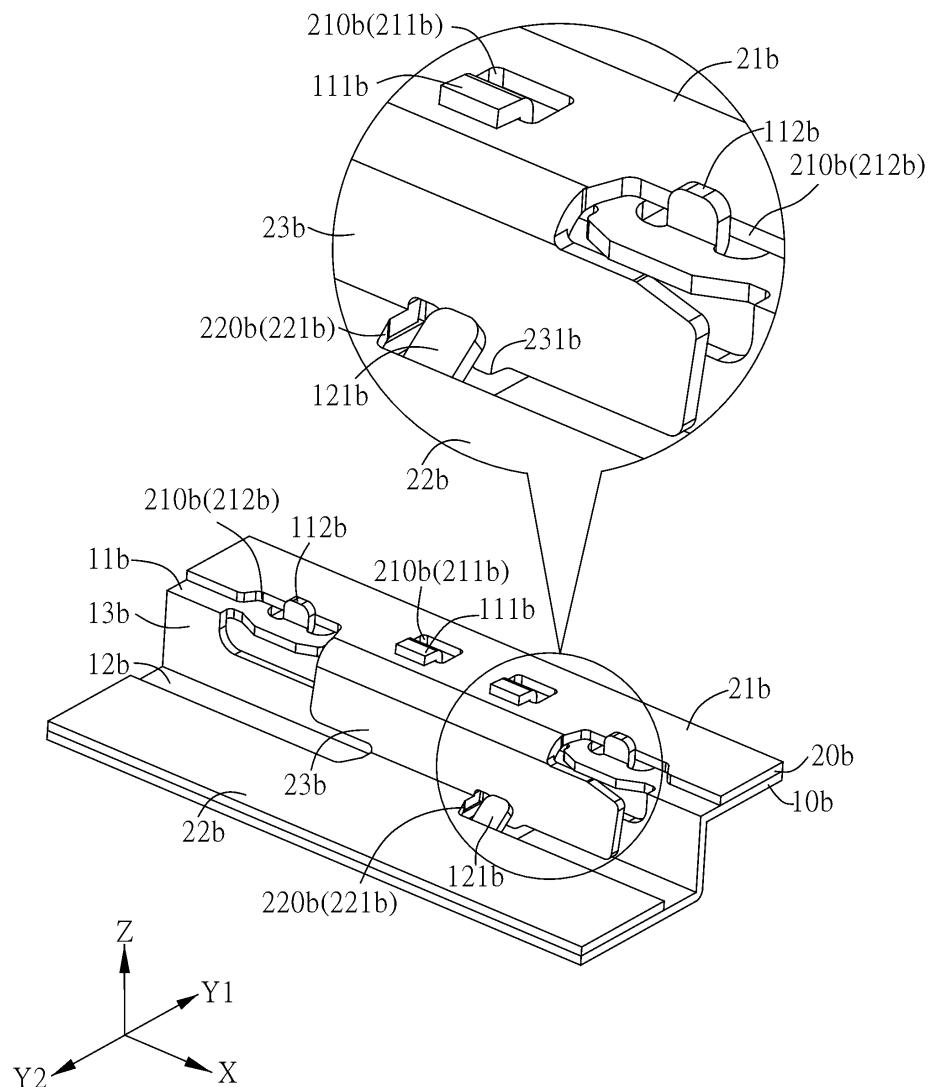

圖 1 為習知具有階梯狀底板之鍵盤的示意圖。圖 2 為本發明之一實施例之鍵盤的部分示意圖。圖 3A 為圖 2 所示之底板及薄膜電路板的部分放大示意圖。圖 3B 為圖 3A 所示之底板及薄膜電路板的分解示意圖。圖 4A 為本發明之第二實施例之底板及薄膜電路板的部分放大示意圖。圖 4B 為圖 4A 所示之底板及薄膜電路板的分解示意圖。圖 5 為本發明之第三實施例之底板及薄膜電路板的部分放大示意圖。圖 6 為本發明之第四實施例之底板及薄膜電路板的部分放大示意圖。

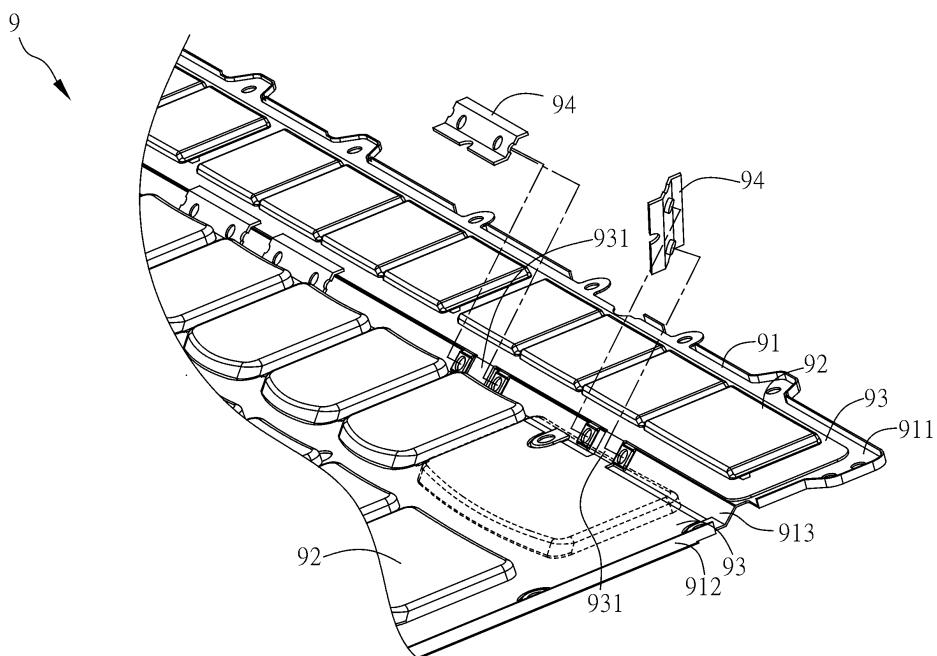

圖 1

(3)

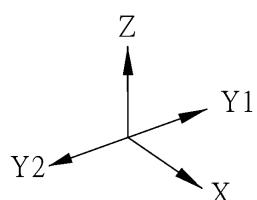

圖2

(4)

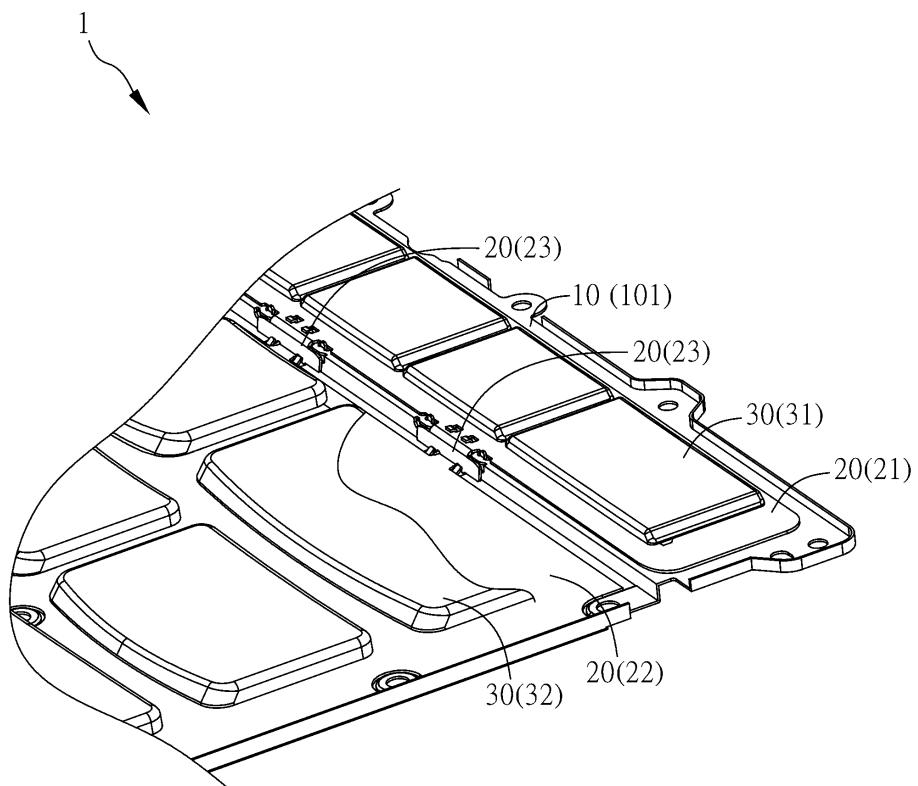

圖3A

(5)

圖3B

(6)

圖 4A

圖4B

圖 5

(9)

圖6