【11】證書號數：I658559

【45】公告日：中華民國 108 (2019) 年 05 月 01 日

|                |                             |                            |

|----------------|-----------------------------|----------------------------|

| 【51】Int. Cl. : | <i>H01L23/538 (2006.01)</i> | <i>H04B10/80 (2013.01)</i> |

|                | <i>H04B10/50 (2013.01)</i>  | <i>H04B10/60 (2013.01)</i> |

發明

全 9 頁

【54】名稱：具有光學互連結構的半導體封裝、包含其之記憶卡及包含其之電子系統

SEMICONDUCTOR PACKAGES WITH OPTICAL INTERCONNECTION

STRUCTURES, MEMORY CARDS INCLUDING THE SAME, AND

ELECTRONIC SYSTEMS INCLUDING THE SAME

【21】申請案號：104114113      【22】申請日：中華民國 104 (2015) 年 05 月 04 日

【11】公開編號：201630370      【43】公開日期：中華民國 105 (2016) 年 08 月 16 日

【30】優先權：2014/11/17      南韓      10-2014-0160277

【72】發明人：金鍾薰 (KR) KIM, JONG HOON

【71】申請人：南韓商愛思開海力士有限公司      SK HYNIX INC.

南韓

【74】代理人：閻啟泰；林景郁

【56】參考文獻：

|                        |                        |

|------------------------|------------------------|

| US      7982305B1      | US      2004/0208593A1 |

| US      2008/0180389A1 | US      2014/0169801A1 |

審查人員：賴恩賞

## 【57】申請專利範圍

- 一種半導體封裝，包括：一半導體晶片，設置在一中介層的頂表面上；一第一驅動器晶片和一第二驅動器晶片，分別設置在所述中介層的頂表面和的底表面上；一第一光學發送器和一第一光學接收器，安裝在所述第一驅動器晶片的表面上且藉由所述第一驅動器晶片所控制；以及一第二光學發送器和一第二光學接收器，安裝在所述第二驅動器晶片的表面上且藉由所述第二驅動器晶片所控制，其中所述第二光學發送器和所述第二光學接收器與所述第一光學發送器和所述第一光學接收器透過穿透所述中介層的光信號來進行光學通訊，其中該中介層包含：一第一導電互連線，用於將所述半導體晶片電耦接到所述第一驅動器晶片；一信號端子，設置在所述中介層的底表面上；以及一第二導電互連線，用於將所述第二驅動器晶片電耦接到所述信號端子。

- 根據申請專利範圍第 1 項的半導體封裝，其中所述第一和第二驅動器晶片被設置成與所述中介層的一部分重疊以面對彼此。

- 根據申請專利範圍第 2 項的半導體封裝，其中所述第一光學發送器和所述第一光學接收器被安裝在面對所述第二驅動器晶片的所述第一驅動器晶片的一表面上。

- 根據申請專利範圍第 3 項的半導體封裝，其中，所述第二光學接收器被安裝在面對所述第一驅動器晶片的所述第二驅動器晶片的一表面上，並且與所述第一光學發送器對準，使得從所述第一光學發送器產生的第一光信號穿透所述中介層而到達所述第二光學接收器；以及其中，所述第二光學發送器被安裝在面對所述第一驅動器晶片的所述第二驅動器晶片的一表面上，並且與所述第一光學接收器對準，使得從所述第二光學發送器產生的第二光信號穿透所述中介層而到達所述第一光學接收器。

- 根據申請專利範圍第 4 項的半導體封裝，其中所述中介層包括透明光穿透部分，所述第一和第二光信號通過所述透明光穿透部分而穿過。

6. 根據申請專利範圍第 4 項的半導體封裝，其中所述中介層包括矽材料，其中所述第一和第二光信號通過所述矽材料。

7. 根據申請專利範圍第 6 項的半導體封裝，其中所述第一和第二光信號為紅外(IR)射線。

8. 根據申請專利範圍第 7 項的半導體封裝，其中所述第一和第二光信號具有 1200 奈米至 15000 奈米的波長。

9. 根據申請專利範圍第 4 項的半導體封裝，其中所述第一和第二光信號透過穿透所述中介層的通孔所發送。

10. 根據申請專利範圍第 1 項的半導體封裝，其中所述半導體晶片包括記憶體晶片、中央處理單元(CPU)晶片、系統大型積體電路(LSI)晶片或現場可程式閘陣列(FPGA)晶片。

11. 根據申請專利範圍第 1 項的半導體封裝，其中所述第一光學發送器包括一雷射裝置，並且所述第一光學接收器包括一光偵測器。

12. 根據申請專利範圍第 11 項的半導體封裝，其中，所述第一驅動器晶片控制所述雷射裝置，使得所述雷射裝置將自所述半導體晶片輸出的電信號轉換成所述光信號中的一者；或其中，所述第一驅動器晶片控制所述光偵測器以將另一個光信號轉換成電信號，並且將所述電信號發送至所述半導體晶片。

13. 根據申請專利範圍第 1 項的半導體封裝，進一步包括：穿透所述中介層的第一貫孔；以及一第三導電互連線，設置在所述中介層的頂表面，以將所述第一貫孔的一端電耦接到所述第一驅動器晶片。

14. 根據申請專利範圍第 13 項的半導體封裝，進一步包括：一電源供應端子，設置在所述中介層的底表面並且電耦接到所述第一貫孔的另一端。

15. 根據申請專利範圍第 14 項的半導體封裝，進一步包括：一第四導電互連線，設置在所述中介層的底表面上以將所述電源供應端子電耦接到所述第二驅動器晶片。

16. 根據申請專利範圍第 13 項的半導體封裝，進一步包括：另一信號端子，設置在所述中介層的底表面上並且電耦接到所述第一貫孔的另一端。

17. 根據申請專利範圍第 15 項的半導體封裝，進一步包括：穿透所述中介層的第二貫孔；以及一第五導電互連線，設置在所述中介層的頂表面，以將所述第二貫孔的一端電耦接到所述半導體晶片。

18. 一種半導體封裝，包括：一第一驅動器晶片和一第二驅動器晶片，分別設置在一中介層的頂表面和底表面上；一第一半導體晶片，設置在所述中介層的頂表面上且電耦接到所述第一驅動器晶片；一第二半導體晶片，設置在所述中介層的底表面上且電耦接至所述第二驅動器晶片；第一導電互連線，用於將所述第一半導體晶片電耦接到所述第一驅動器晶片；第六導電互連線，用於將所述第二半導體晶片電耦接到所述第二驅動器晶片；一第一光學發送器和一第一光學接收器，安裝在所述第一驅動器晶片的一表面上且藉由所述第一驅動器晶片控制；一第二光學發送器和一第二光學接收器，安裝在所述第二驅動器晶片的一表面上且藉由所述第二驅動器晶片控制；一信號端子，設置在所述中介層的底表面上；以及一第二導電互連線，用於將第二驅動器晶片電耦接到所述信號端子，其中所述第二光學發送器和所述第二光學接收器與所述第一光學發送器和所述第一光學接收器透過穿透所述中介層的光信號進行光學通訊。

19. 一種半導體封裝，包括：一第一驅動器晶片和一第二驅動器晶片，分別設置在一中介層的頂表面和底表面上；一第一半導體晶片，設置在所述中介層的頂表面上且電耦接到所述第一驅動器晶片；一第二半導體晶片，設置在所述中介層的頂表面上且與所述第一半導體晶片分隔開；第一導電互連線，用於將所述第一半導體晶片電耦接到所述第一驅動器晶片；一第一光學發送器和一第一光學接收器，安裝在所述第一驅動器晶片的一表面

上且藉由所述第一驅動器晶片控制；一第二光學發送器和一第二光學接收器，安裝在所述第二驅動器晶片的一表面上且藉由所述第二驅動器晶片控制；信號端子，設置在所述中介層的所述底表面上；一第二導電互連線，用於將第二驅動器晶片電耦接到所述信號端子中的一者；以及一第三貫孔，穿透所述中介層以電耦接所述第二半導體晶片到所述信號端子的另一者，其中所述第二光學發送器和所述第二光學接收器與所述第一光學發送器和所述第一光學接收器透過穿透所述中介層的光信號進行光學通訊。

#### 圖式簡單說明

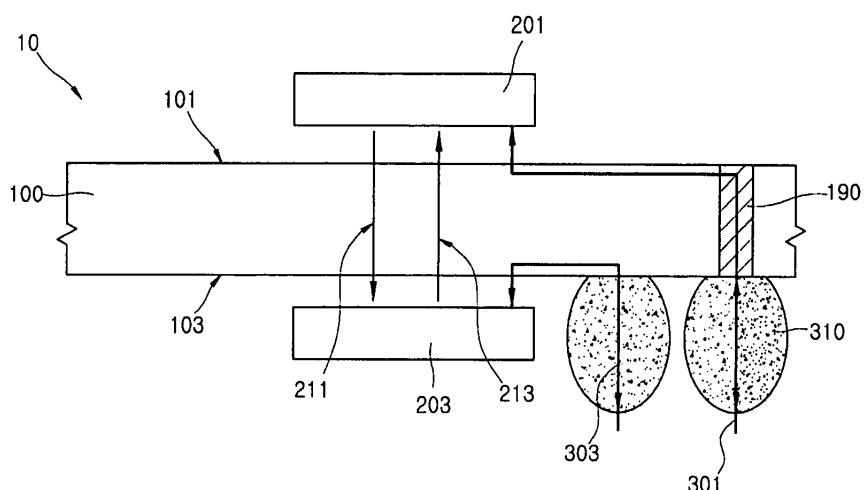

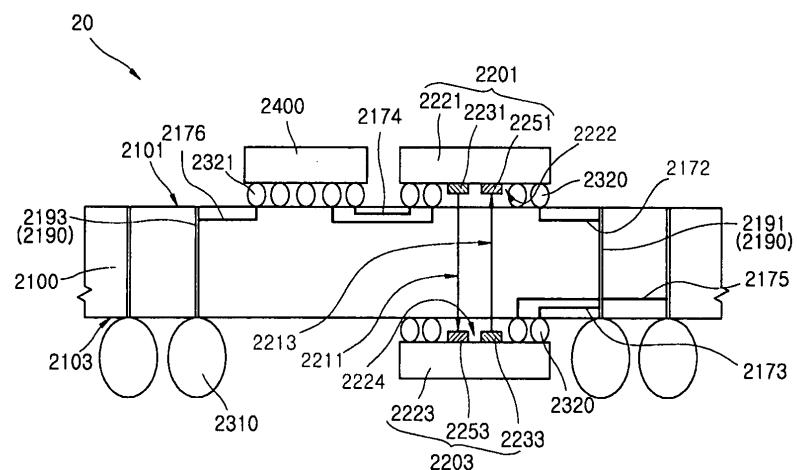

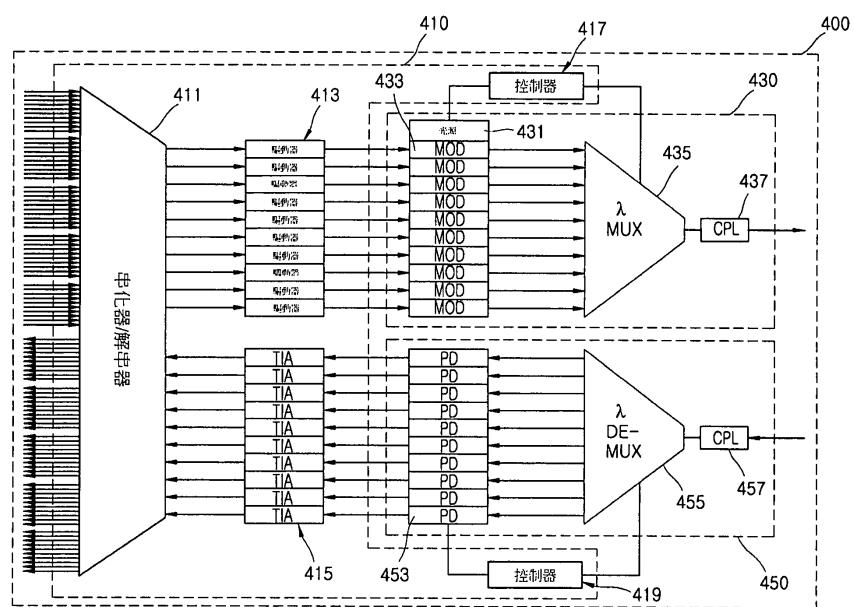

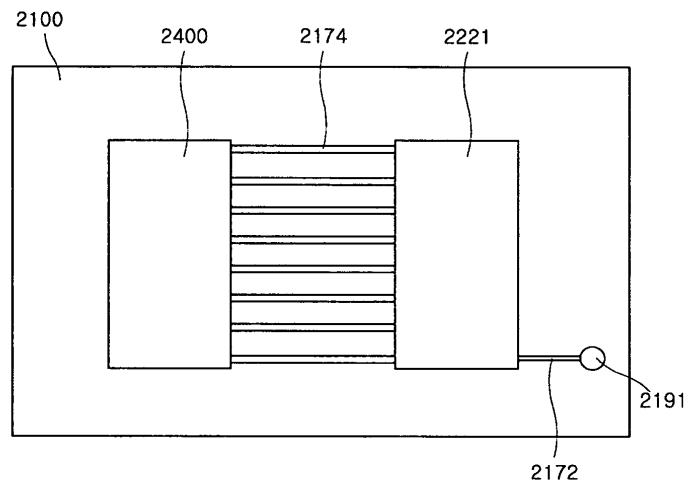

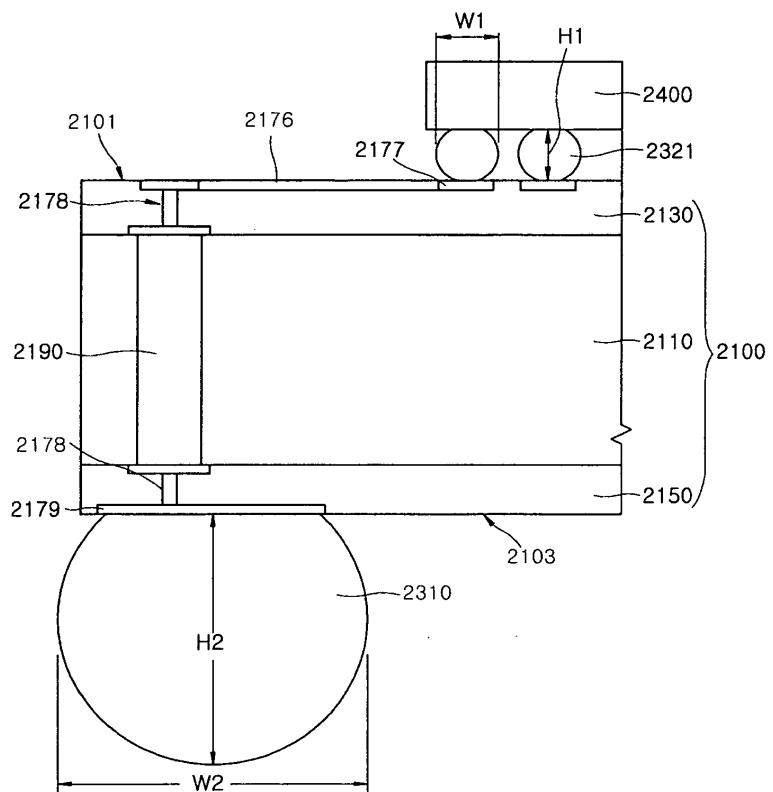

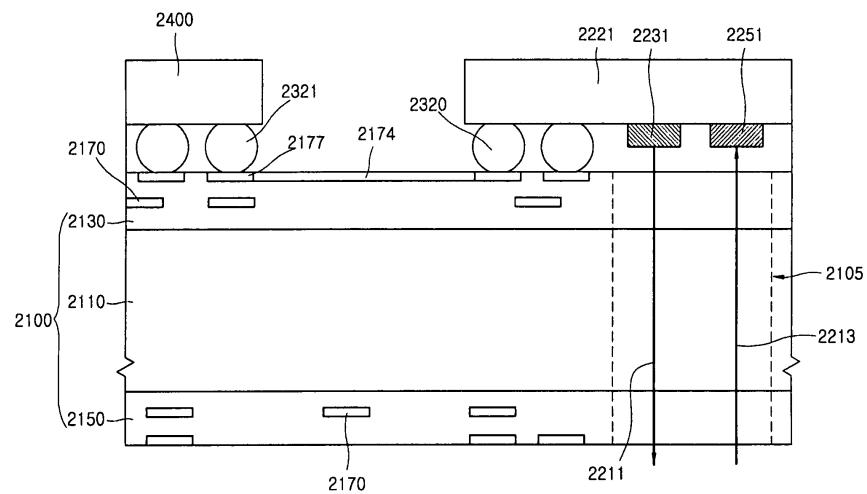

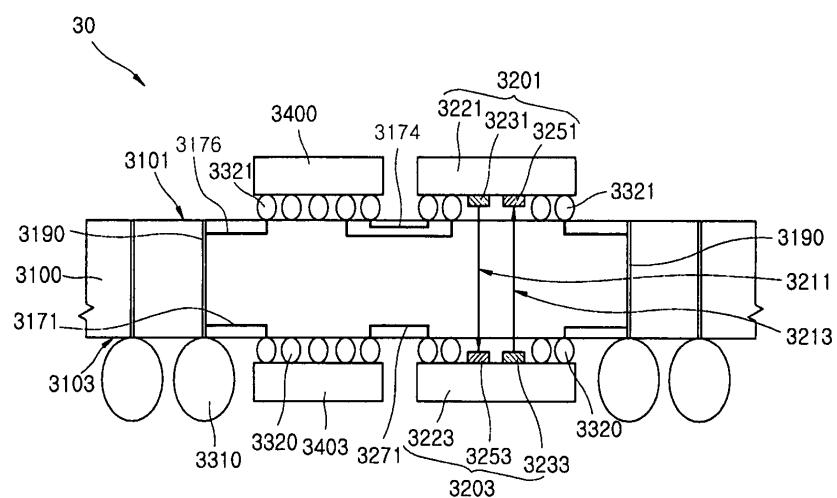

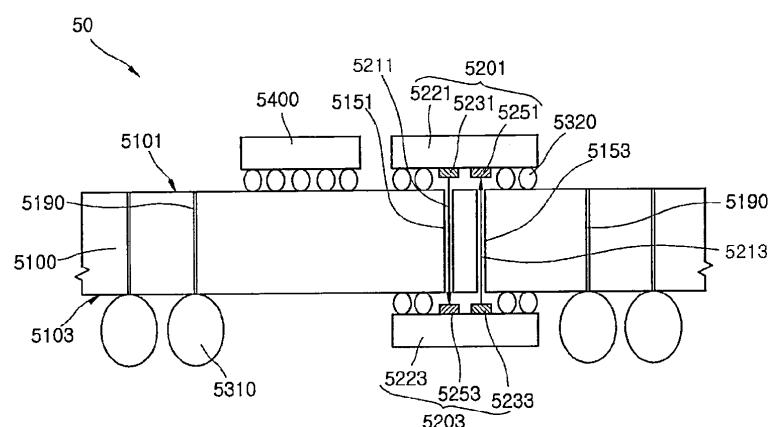

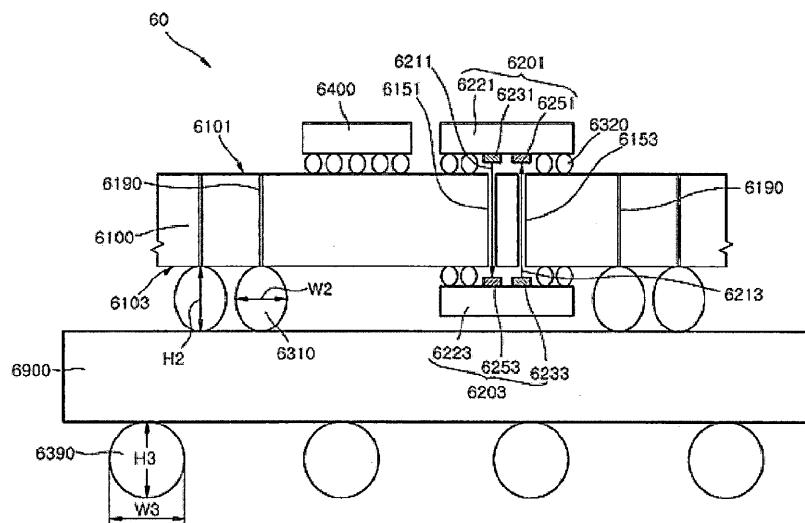

圖 1 是示出根據一實施例的半導體封裝的橫截面圖；圖 2 是示出根據一實施例的半導體封裝的橫截面圖；圖 3 是示出包括在根據一實施例的半導體封裝中的電-光-電收發器之一方框圖；圖 4 是示出包括在根據一實施例的半導體封裝中的半導體晶片和驅動器晶片之間的電連接之一平面圖；圖 5 是示出包括在根據一實施例的半導體封裝中的半導體晶片和中介層之間的電連接的橫截面圖；圖 6 是示出包括在根據一實施例的半導體封裝中的驅動器晶片和中介層之間的電連接的橫截面圖；圖 7 是示出根據另一實施例的半導體封裝的橫截面圖。

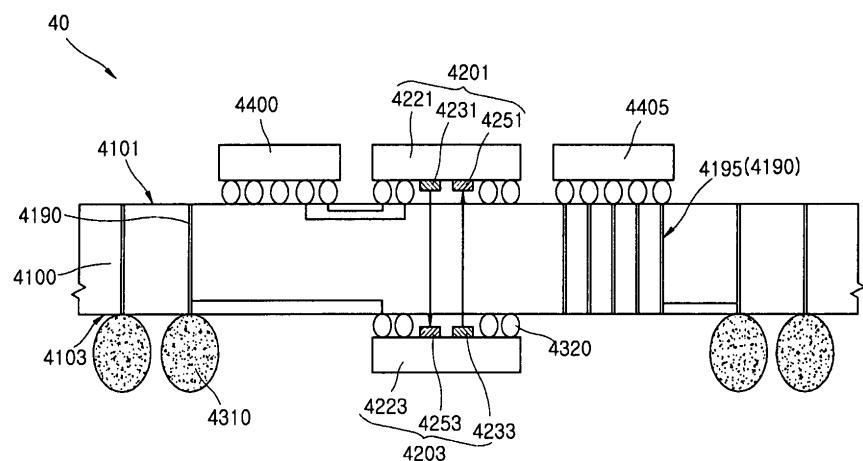

圖 8 是示出根據再一實施例的半導體封裝的橫截面圖；圖 9 是示出根據又一實施例的半導體封裝的橫截面圖。

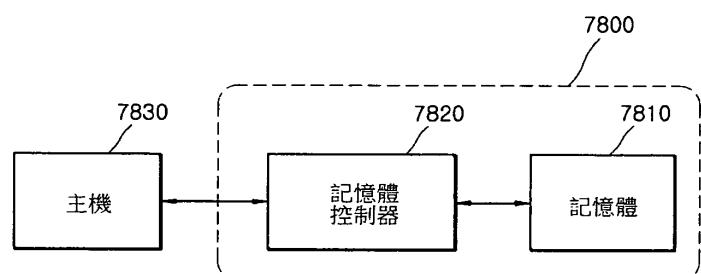

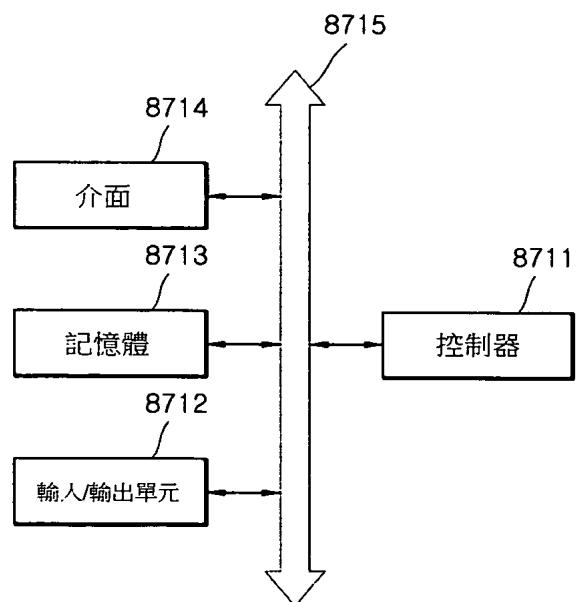

圖 10 是示出根據一實施例的半導體封裝的橫截面圖；圖 11 是示出採用包括根據一些實施例的至少一個半導體封裝的記憶卡的電子系統之一方框圖；以及圖 12 是示出包含根據一些實施例的至少一個半導體封裝的另一電子系統之一方框圖。

圖1

圖2

圖3

(5)

圖4

圖5

圖6

圖7

圖8

圖9

圖10

圖11

8710

圖12