【11】證書號數：I653580

【45】公告日：中華民國 108 (2019) 年 03 月 11 日

【51】Int. Cl. : *G06F9/44 (2018.01)* *G06F13/38 (2006.01)*

*G06F15/163 (2006.01)*

發明

全 6 頁

【54】名稱：具有多主控晶片的主機板及切換控制順序的方法

MOTHER BOARD WITH MULTI MASTER CONTROL CHIPS AND THE

METHOD SWITCHING THE CONTROLLING ORDER

【21】申請案號：106135215 【22】申請日：中華民國 106 (2017) 年 10 月 13 日

【72】發明人：張燕雲 (TW) CHANG, YEN-YUN；孫培華 (TW) SUN, PEI-HUA；簡源利

(TW) CHIEN, YUAN-LI；陳凱勛 (TW) CHEN, KAI-HSUN【71】申請人：技嘉科技股份有限公司 GIGA-BYTE TECHNOLOGY CO., LTD.

新北市新店區寶強路 6 號

【74】代理人：李文賢；楊慶隆

【56】參考文獻：

TW 200619967

TW 200928719

US 2006/0129789A1

審查人員：游象甫

【57】申請專利範圍

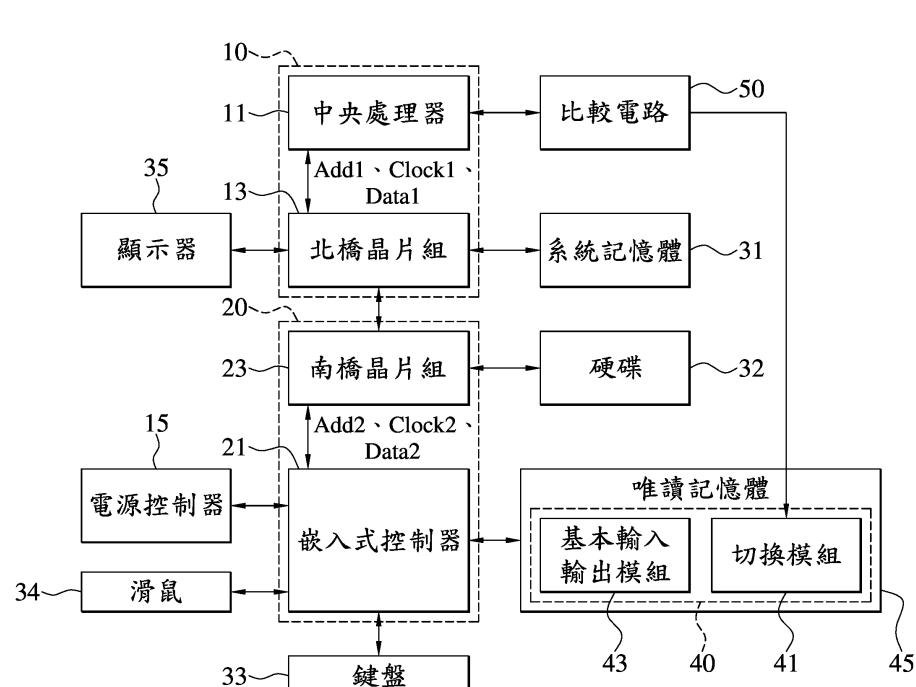

- 一種具有多主控晶片的主機板，包含：一第一主控晶片組，用以輸出複數個第一驅動信號，其中該等第一驅動信號中包含一第一資料信號；一第二主控晶片組，用以輸出複數個第二驅動信號；複數個受控硬體，電性連接至該第一主控晶片組以及該第二主控晶片組，接收該等第一驅動信號或該等第二驅動信號，並根據該等第一驅動信號或該等第二驅動信號而作動；一基本輸入輸出系統(BIOS)，包含一基本輸入輸出模組、以及一切換模組，該基本輸入輸出模組用以偵測該第一主控晶片組、該第二主控晶片組、以及該等受控硬體的狀態，該切換模組電性連接該第一主控晶片組及該第二主控晶片組，並偵測該第一主控晶片組的作動狀態，判斷該第一主控晶片組是否輸出該第一資料信號，當該第二主控晶片組準備作動時，並判斷該第一主控晶片組輸出該第一資料信號時，該切換模塊產生一停止信號至該第二主控晶片組，使該等第二驅動信號暫時無法發出，而當該第二主控晶片組準備作動時，並判斷該第一主控晶片組不再輸出該第一資料信號時，發出一致能信號至該第二主控晶片組，使該等第二驅動信號發出；以及一比較電路，連接該切換模組，該比較電路在該第一主控晶片組輸出該第一資料信號時，輸出一低電壓準位，而在該第一主控晶片組不再輸出該第一資料信號時，輸出一高電壓準位，該切換模組接收到低電壓準位時，產生停止信號，以暫停輸出該第二驅動信號，暫停該第二主控晶片組作動。

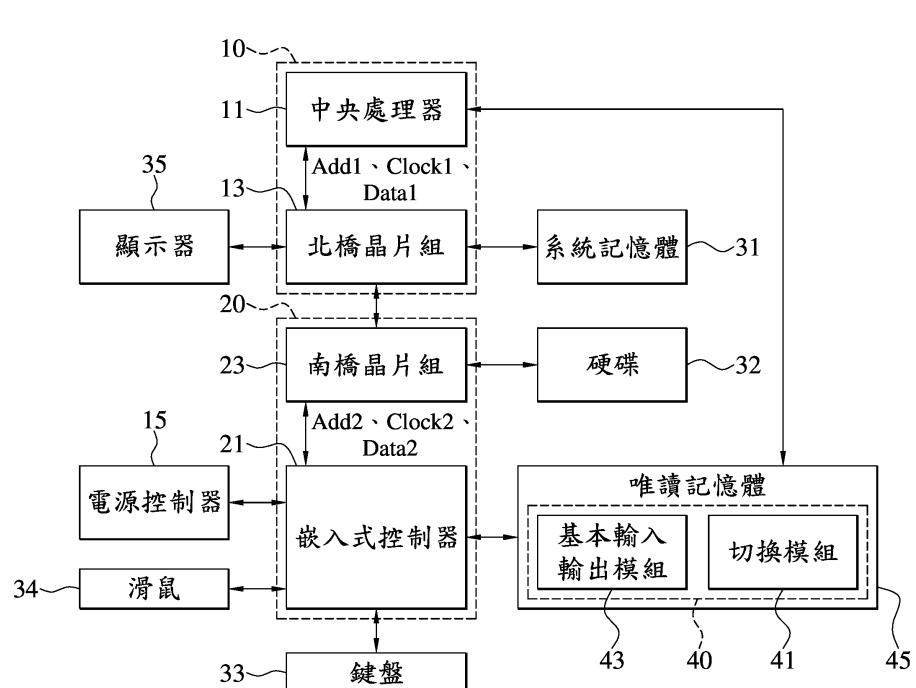

- 如請求項 1 所述之具有多主控晶片的主機板，其中該第一主控晶片組包含一中央處理器以及一北橋晶片組，該第二主控晶片組包含一嵌入式控制器以及一南橋晶片組。

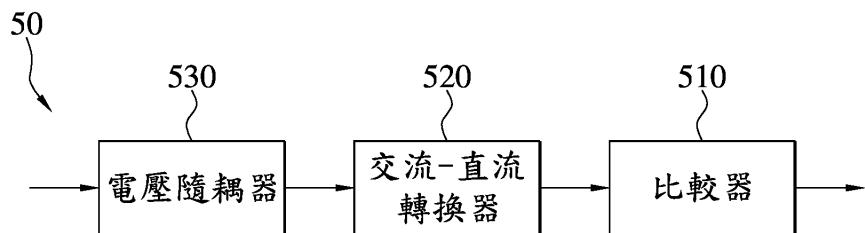

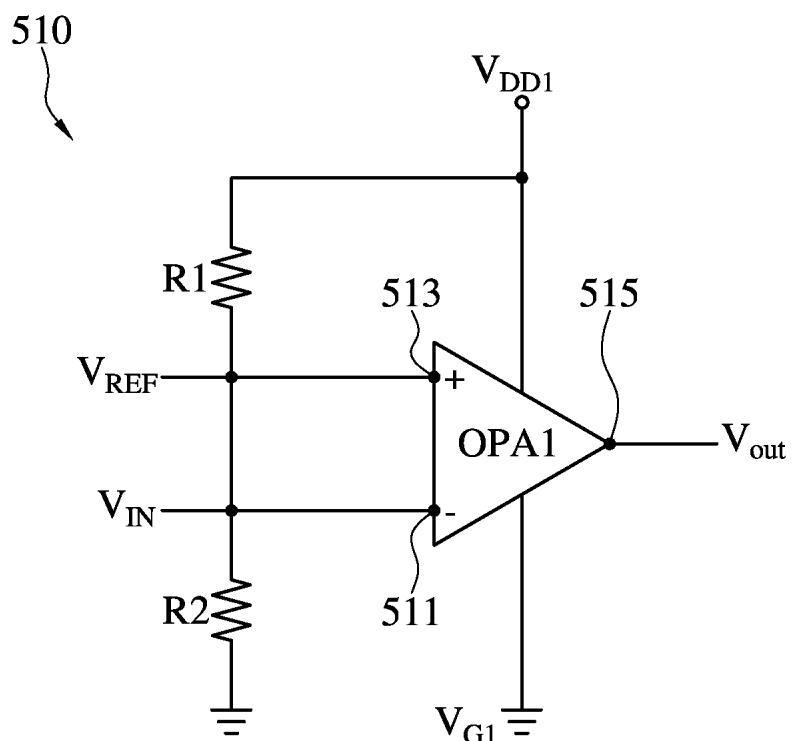

- 如請求項 1 所述之具有多主控晶片的主機板，其中該比較電路包含一比較器，該比較器至少包含一第一輸入端、一第二輸入端、以及一第一輸出端，其中該第一輸入端電性連接該第一主控晶片組，該第二輸入端電性連接一參考電壓，該第一輸出端電性連接該切換模組。

4. 如請求項 1 所述之具有多主控晶片的主機板，其中當該切換模組接收到該高電壓準位時，產生該致能信號。

5. 如請求項 3 所述之具有多主控晶片的主機板，其中該比較電路更包含一交流直流轉換器(AC to DC converter)，該交流直流轉換器包含一第三輸入端及一第三輸出端，其中該第三輸入端電性連接該第一主控晶片組、該第三輸出端電性連接該第一輸入端。

6. 如請求項 5 所述之具有多主控晶片的主機板，更包含一電壓隨耦器，該電壓隨耦器包含一第四輸入端、一第五輸入端、及一第四輸出端，該第四輸入端電性連接該第一主控晶片組，而該第四輸出端電性連接於該第三輸入端及該第五輸入端。

7. 一種切換控制順序的方法，包含：啟動一基本輸入輸出系統，執行一系統初始化作業；以該基本輸入輸出系統以及一比較電路偵測一第一主控晶片組及一第二主控晶片組的作動狀態，並偵測該第一主控晶片組是否輸出一第一資料信號，該比較電路在該第一主控晶片組輸出該第一資料信號時，輸出一低電壓準位，而在該第一主控晶片組不再輸出該第一資料信號時，輸出一高電壓準位；當偵測第二主控晶片組的準備作動，並判斷該第一主控晶片組輸出該第一資料信號時，以該基本輸入輸出系統產生一停止信號至該第二主控晶片組，使該第二主控晶片組停止作動；當判斷該第二主控晶片組的準備作動，並判斷該第一主控晶片組不再輸出該第一資料信號時，以該基本輸入輸出系統產生一致能信號至該第二主控晶片組，致能該第二主控晶片組作動；以及當該基本輸入輸出系統接收到來自該比較電路輸出該低電壓準位時，產生該停止信號至該第二主控晶片組，暫停該第二主控晶片組作動。

8. 如請求項 7 所述之切換控制順序的方法，其中當該基本輸入輸出系統接收到該低電壓準位時，產生該停止信號，而該基本輸入輸出系統接收到該高電壓準位時，產生該致能信號。

#### 圖式簡單說明

通過參照附圖進一步詳細描述本發明的示例性實施例，本發明的上述和其他示例性實施例，優點和特徵將變得更加清楚，其中：圖 1 為具有多主控晶片的主機板第一實施例的單元示意圖。

圖 2 為具有多主控晶片的主機板第二實施例的單元示意圖。

圖 3 為圖 2 中比較電路的單元示意圖。

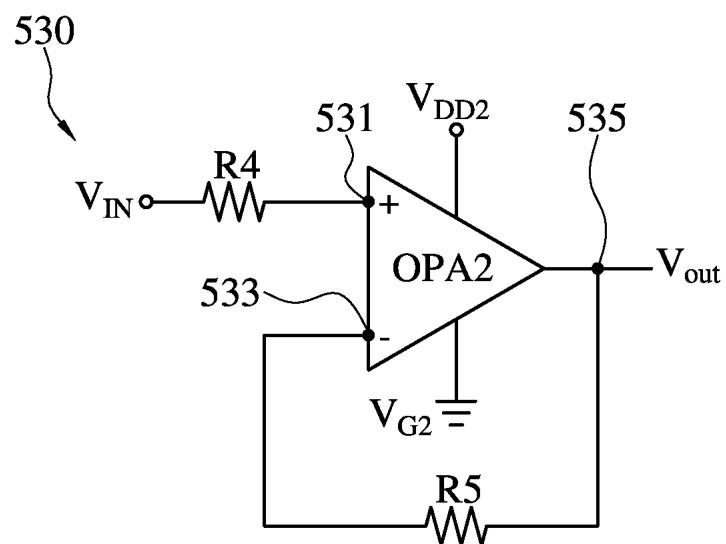

圖 4 為圖 3 中比較器的電路示意圖。

圖 5 為圖 3 中交流-直流轉換器的電壓示意圖。

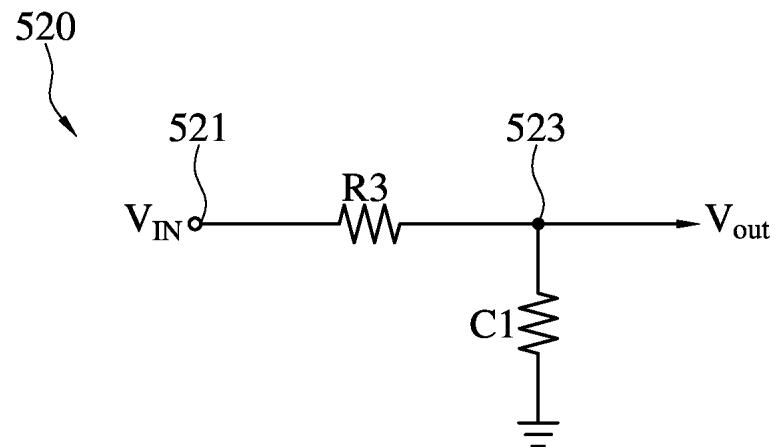

圖 6 為圖 3 中電壓隨耦器的電路示意圖。

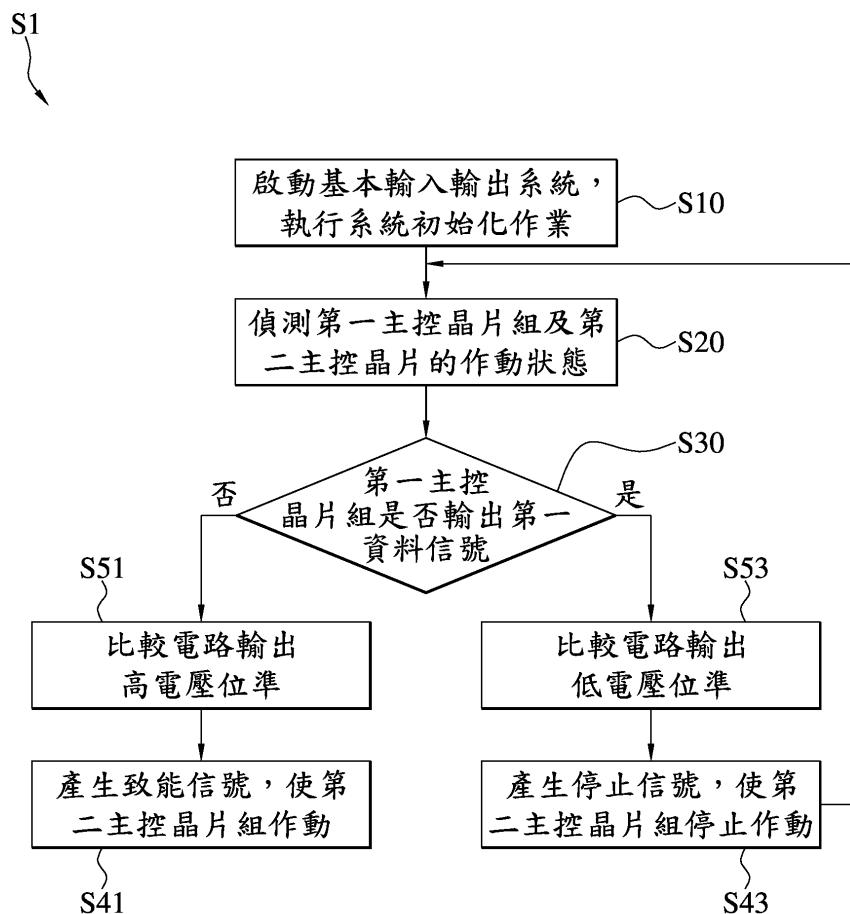

圖 7 為切換控制順序的方法的流程圖。

1

圖 2

(4)

圖3

圖4

(5)

圖5

圖6

圖7