【11】證書號數：I643306

【45】公告日：中華民國 107 (2018) 年 12 月 01 日

【51】Int. Cl. : *H01L23/522 (2006.01)* *H01L23/488 (2006.01)*

*H01L23/538 (2006.01)*

發明

全 8 頁

【54】名稱：封裝基板、包含其之半導體封裝、包含其之電子系統及包含其之記憶卡

PACKAGE SUBSTRATES, SEMICONDUCTOR PACKAGES INCLUDING THE SAME, ELECTRONIC SYSTEMS INCLUDING THE SAME, AND MEMORY CARDS INCLUDING THE SAME

【21】申請案號：104116624      【22】申請日：中華民國 104 (2015) 年 05 月 25 日

【11】公開編號：201628154      【43】公開日期：中華民國 105 (2016) 年 08 月 01 日

【30】優先權：2015/01/22      南韓      10-2015-0010833

【72】發明人：金承知 (KR) KIM, SEUNG JEE ; 鄭源德 (KR) JUNG, WON DUCK

【71】申請人：南韓商愛思開海力士有限公司      SK HYNIX INC.

南韓

【74】代理人：閻啟泰；林景郁

【56】參考文獻：

TW      201342550A

TW      201430970A

TW      201431016A

US      2005/0133905A1

US      2009/0057916A1

審查人員：邱迺軒

## 【57】申請專利範圍

- 一種封裝基板，其包括：一基板核心層；複數個第一外部的電路互連線，其被設置在所述基板核心層的一頂表面上，所述複數個第一外部的電路互連線是包含一位在所述基板核心層上並且相鄰所述基板核心層的一邊緣的第一最外側的外部的電路互連線；複數個內部的電路互連線，其被設置在所述基板核心層中，所述複數個內部的電路互連線是包含一位在所述基板核心層中並且相鄰所述基板核心層的所述邊緣的最外側的內部的電路互連線；一第一接合墊，其被設置在所述第一最外側的外部的電路互連線上並且在所述基板核心層的第一接合區域中被露出；以及一第二接合墊，其被設置在所述最外側的內部的電路互連線上並且在所述基板核心層的第二接合區域中被露出，其中所述第一接合區域是和一晶片安裝區域在與該基板核心層的該表面平行的橫向方向上間隔開第一距離，並且所述第二接合區域是和所述晶片安裝區域在與該基板核心層的該表面平行的橫向方向上間隔開第二距離，所述第二距離是大於所述第一距離。

- 如申請專利範圍第 1 項的封裝基板，其中所述第一接合區域是和所述第二接合區域間隔開第三距離。

- 如申請專利範圍第 1 項的封裝基板，其進一步包括複數個被設置在所述基板核心層的一底表面上的第二外部的電路互連線。

- 如申請專利範圍第 3 項的封裝基板，其進一步包括：一第一貫孔，其被配置以電連接所述第一最外側的外部的電路互連線至所述複數個內部的電路互連線中的除了所述最外側的內部的電路互連線之外的一個；一第二貫孔，其被配置以將被連接至所述第一貫孔的所述內部的電路互連線電連接至所述複數個第二外部的電路互連線中的一個；以及一第三貫孔，其被配置以電連接所述最外側的內部的電路互連線至所述複數個第二外部的電

路互連線中的另一個，其中所述第一、第二及第三貫孔只位在所述第二接合區域與所述封裝基板的一中央部分之間。

5. 如申請專利範圍第 3 項的封裝基板，其進一步包括：一第一貫孔，其被設置在所述基板核心層中以電連接所述第一最外側的外部的電路互連線至所述複數個內部的電路互連線中的除了所述最外側的內部的電路互連線之外的一個；一第二貫孔，其被設置在所述基板核心層中以將被連接至所述第一貫孔的所述內部的電路互連線電連接至所述複數個第二外部的電路互連線中的一個；以及一第三貫孔，其被設置在所述基板核心層中以電連接所述最外側的內部的電路互連線至所述複數個第二外部的電路互連線中的另一個。

6. 如申請專利範圍第 5 項的封裝基板，其中所述第一貫孔以及所述第二貫孔是被設置在所述晶片安裝區域中及/或在一介於所述晶片安裝區域與所述第一接合區域之間的介面區域中。

7. 如申請專利範圍第 5 項的封裝基板，其中所述第一最外側的外部的電路互連線中的至少兩個是位在所述基板核心層上並且相鄰所述基板核心層的所述邊緣，以及其中所述第一最外側的外部的電路互連線是從所述晶片安裝區域延伸至位在所述第一接合區域與所述第二接合區域之間的一區域。

8. 如申請專利範圍第 7 項的封裝基板，其中所述第一貫孔中的至少兩個是被設置在所述基板核心層中，以分別電連接所述第一最外側的外部的電路互連線至所述複數個內部的電路互連線中的除了所述最外側的內部的電路互連線之外的一個，其中所述第一貫孔包含位在所述晶片安裝區域與所述第一接合區域之間的偶數第一貫孔、以及位在所述晶片安裝區域中的奇數第一貫孔，以及其中所述偶數及奇數第一貫孔是被配置以形成一曲折圖案。

9. 如申請專利範圍第 5 項的封裝基板，其中所述第三貫孔是被設置在所述晶片安裝區域與所述第二接合區域之間。

10. 如申請專利範圍第 5 項的封裝基板，其中所述最外側的內部的電路互連線中的至少兩個是位在所述基板核心層中並且相鄰所述基板核心層的所述邊緣，以及其中所述最外側的內部的電路互連線是從介於所述基板核心層的一側壁與所述第二接合區域之間的一區域延伸到介於所述晶片安裝區域與所述第一接合區域之間的一區域。

11. 如申請專利範圍第 10 項的封裝基板，其中所述第三貫孔中的至少兩個是被設置在所述基板核心層中，以分別電連接所述最外側的內部的電路互連線至所述複數個第二外部的電路互連線中的另一個，其中所述第三貫孔是沿著與所述第一接合區域平行的一方向，以一種曲折方式交替地加以排列，並且被設置在所述晶片安裝區域與所述第二接合區域之間。

12. 如申請專利範圍第 11 項的封裝基板，其中所述第三貫孔的每一個是至少部分位在所述第一接合區域之內，以及其中所述最外側的內部的電路互連線是完全重疊所述第三貫孔。

13. 如申請專利範圍第 3 項的封裝基板，其進一步包括一第一絕緣層，所述第一絕緣層是被設置在所述基板核心層的頂表面上以覆蓋所述複數個第一外部的電路互連線，其中所述第一絕緣層是具有一第一開口以及一第二開口。

14. 如申請專利範圍第 13 項的封裝基板，其中所述第一開口以及所述第二開口分別露出在所述第一接合區域中的所述第一接合墊、以及在所述第二接合區域中的所述第二接合墊。

15. 如申請專利範圍第 14 項的封裝基板，其中所述第一開口的一深度是對應於所述第一絕緣層的一頂表面到所述第一接合墊的一頂表面，並且是小於所述第一絕緣層的一厚度。

16. 如申請專利範圍第 15 項的封裝基板，其中所述第二開口的一深度是對應於所述第一絕緣層的頂表面到所述第二接合墊的一頂表面，並且是大於所述第一絕緣層的所述厚度。

17. 如申請專利範圍第 13 項的封裝基板，其中所述基板核心層是具有與所述第二開口垂直地對齊的一溝槽，所述第二開口是貫穿在所述第二接合區域中的所述第一絕緣層。

18. 如申請專利範圍第 17 項的封裝基板，其中所述第二接合墊是藉由所述第二開口以及所述溝槽而被露出。

19. 如申請專利範圍第 18 項的封裝基板，其中所述溝槽的一深度是實質等於一第一高度，所述第一高度是對應於在所述內部的電路互連線的頂表面以及所述第一外部的電路互連線的底表面之間的一高度差。

20. 如申請專利範圍第 13 項的封裝基板，其進一步包括一第二絕緣層，所述第二絕緣層是被設置在所述基板核心層的底表面上以覆蓋所述複數個第二外部的電路互連線，其中所述第二絕緣層是包含一第三開口，所述第三開口是被配置以露出所述複數個第二外部的電路互連線的任一個的一部分。

21. 如申請專利範圍第 20 項的封裝基板，其中所述第三開口是被配置以容許焊料球能夠被設置在所述複數個第二外部的電路互連線的所述露出的部分上。

22. 一種半導體封裝，其包括：一基板核心層；複數個第一外部的電路互連線，其被設置在所述基板核心層的一頂表面上，所述複數個第一外部的電路互連線是包含位在所述基板核心層上並且相鄰所述基板核心層的一邊緣的一第一最外側的外部的電路互連線；複數個內部的電路互連線，其被設置在所述基板核心層中，所述複數個內部的電路互連線是包含位在所述基板核心層中並且相鄰所述基板核心層的所述邊緣的一最外側的內部的電路互連線；一第一接合墊，其被設置在所述第一最外側的外部的電路互連線上並且在所述基板核心層的一第一接合區域中被露出；一第二接合墊，其被設置在所述最外側的內部的電路互連線上並且在所述基板核心層的一第二接合區域中被露出；一第一晶片以及一第二晶片，其依序地被堆疊在所述基板核心層的一晶片安裝區域上；一第一導線，其電連接所述第一晶片的一第一晶片墊至所述第一接合墊；以及一第二導線，其電連接所述第二晶片的一第二晶片墊至所述第二接合墊，其中所述第一接合區域是和一晶片安裝區域在與該基板核心層的該表面平行的橫向方向上間隔開一第一距離，並且所述第二接合區域是和所述晶片安裝區域在與該基板核心層的該表面平行的橫向方向上間隔開一第二距離，所述第二距離是大於所述第一距離。

#### 圖式簡單說明

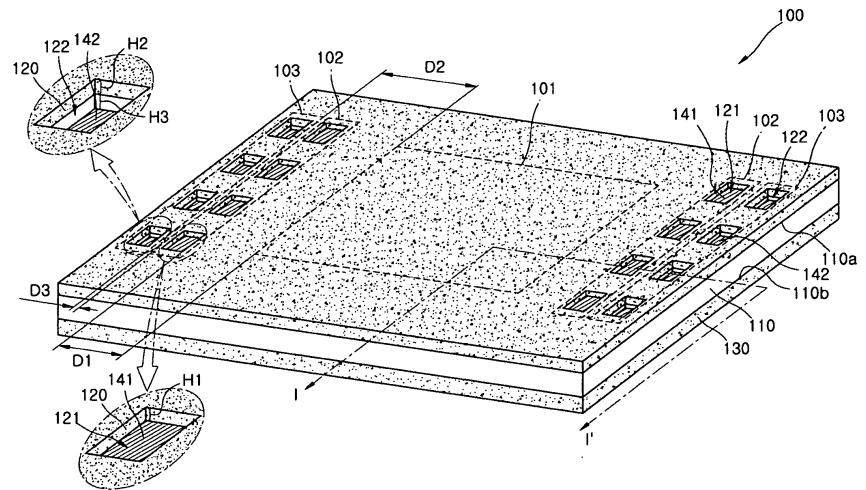

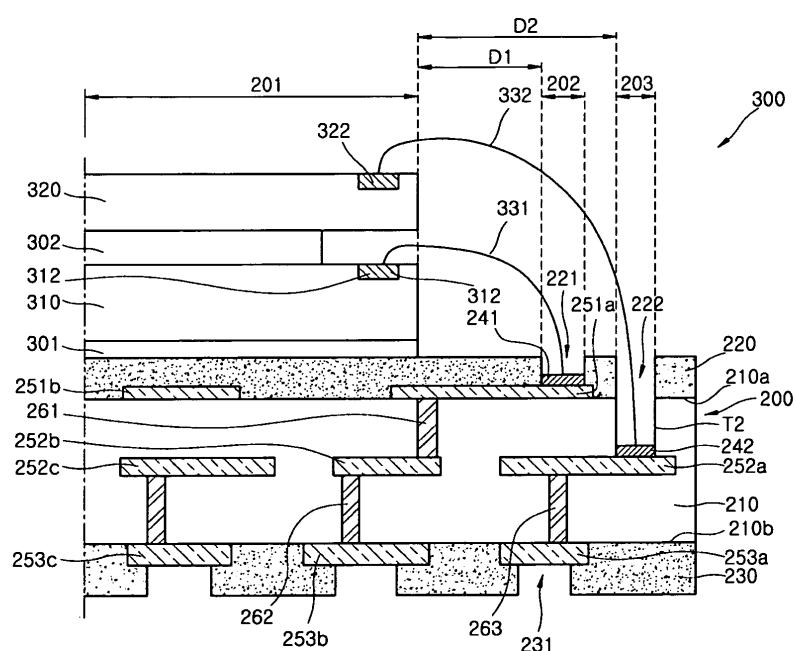

圖 1 是描繪根據一實施例的一種封裝基板的一個例子的一表示的立體圖。

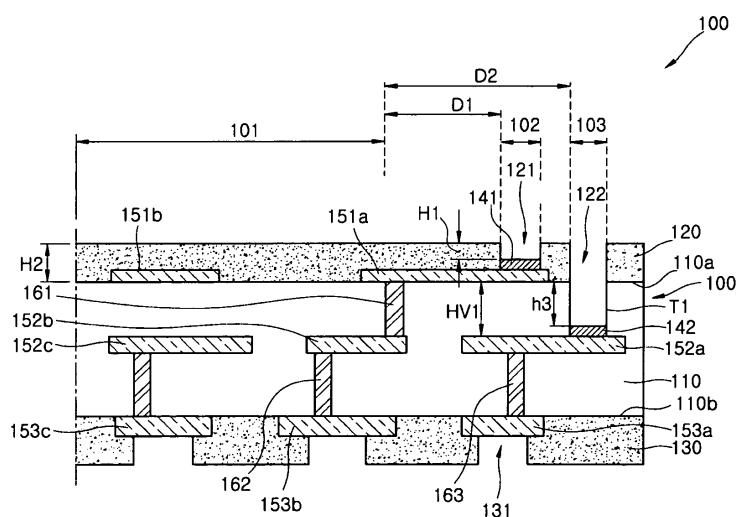

圖 2 是沿著圖 1 的一線 I-I'所取的視圖的一個例子的橫截面表示。

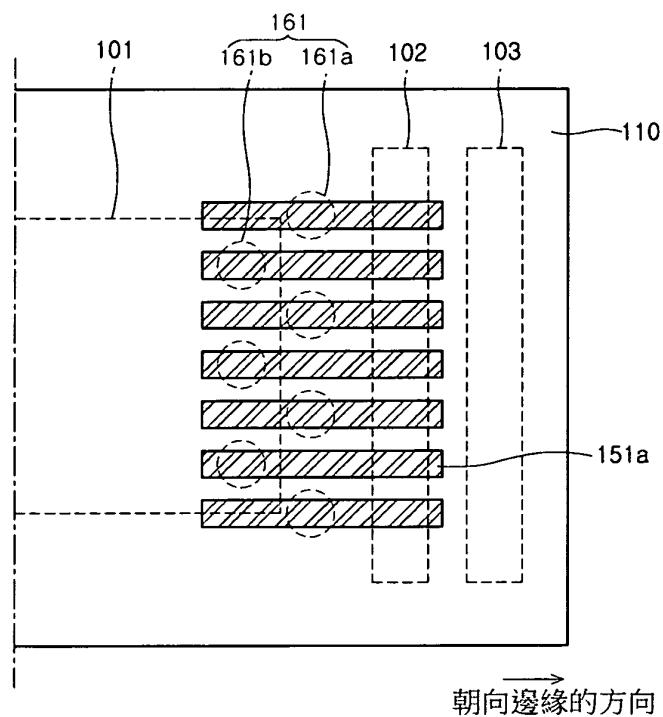

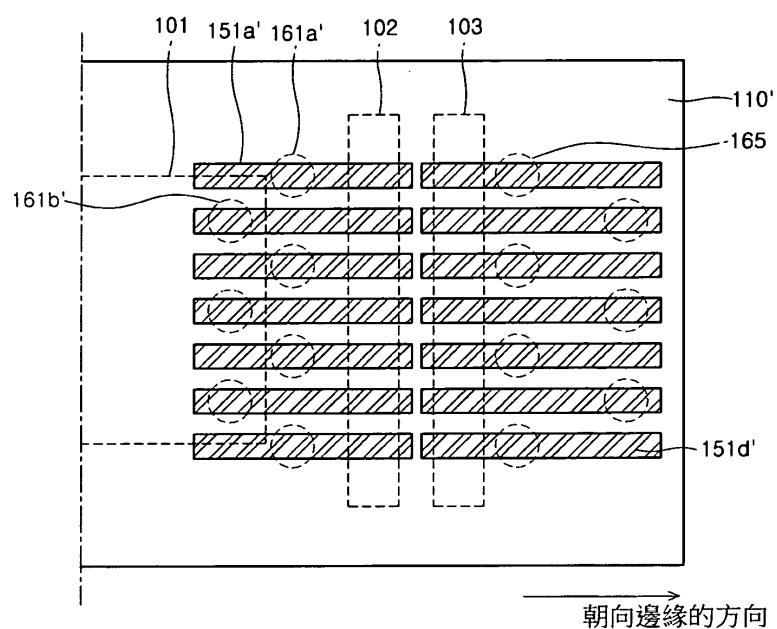

圖 3 是描繪內含在根據一實施例的一種封裝基板中的第一貫孔的位置的一個例子的一表示的平面圖。

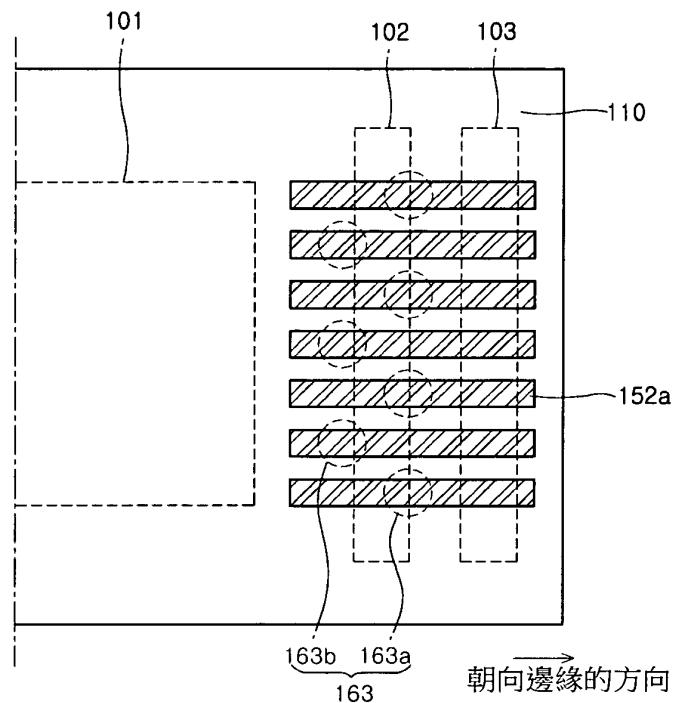

圖 4 是描繪內含在根據一實施例的一種封裝基板中的第三貫孔的位置的一個例子的一表示的平面圖。

圖 5 是描繪用以描述在圖 1 中所描繪的一種封裝基板的優點的一般的封裝基板的一個例子的一表示的平面圖。

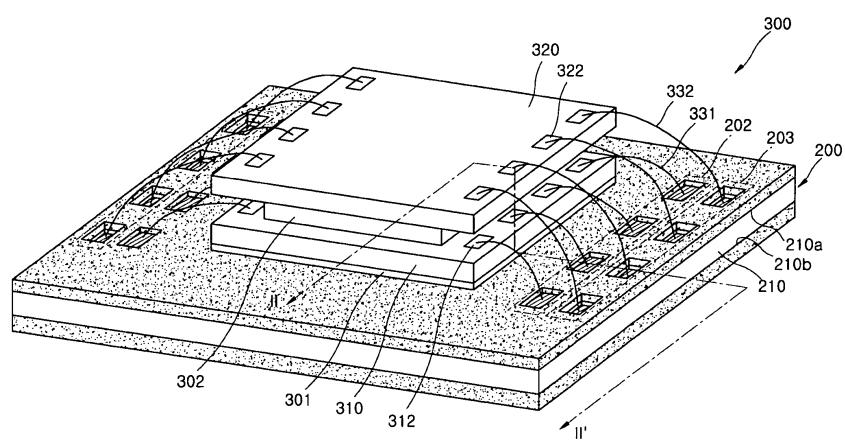

圖 6 是描繪根據一實施例的一種半導體封裝的一個例子的一表示的立體圖。

圖 7 是沿著圖 6 的一線 - '所取的視圖的一個例子的橫截面表示。

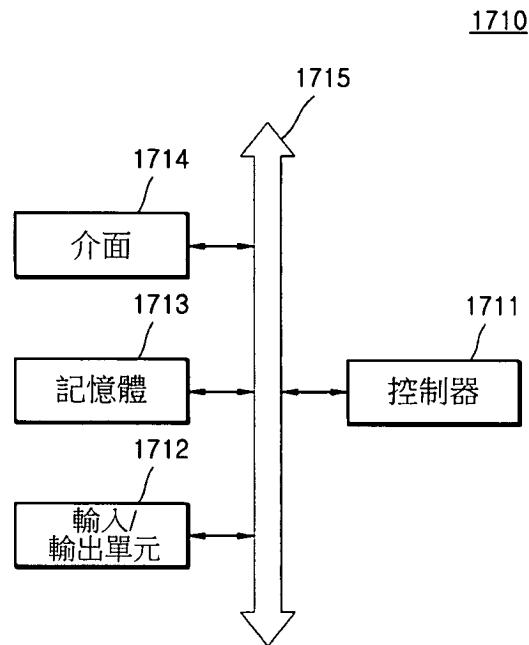

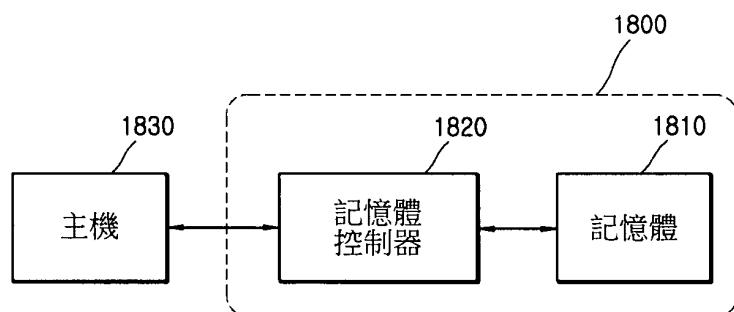

圖 8 是描繪一種包含根據某些實施例的半導體封裝中的至少一個的電子系統的一個例子的一表示的方塊圖。

圖 9 是描繪一種包含根據某些實施例的半導體封裝中的至少一個的電子系統的一個例子的一表示的方塊圖。

(4)

圖1

圖2

圖3

(6)

圖4

圖5

圖6

圖7

圖8

圖9